搜寻

- 04/02/2024

超越毫厘之争,掌握微小化的艺术

随着电子产品微小化的需求不断提升,封装技术也必须朝向更小、更高效的方向发展。先进封装技术能够将多颗裸晶、主动元件、被动元件甚至机电元件整合到单一微型封装体中,在缩小尺寸的同时,也能提升效能和整体系统功能。在开始探讨先进封装技术之前,您可以先阅读另一篇文章:系统级封装(SiP) : 一站式微小化解决方案。本文将接着深入探讨系统级封装 (SiP) 技术,并介绍其复杂的组装流程,以及其他先进封装技术,例如系统单晶片 (SoC) 和小晶片模组 (Chiplet) 技术。

系统级封装SiP制程步骤拆解

SiP系统级封装制造过程涉及几个关键步骤,通过遵循这些细致的步骤,制造商可以确保各种电子设备中使用的 SiP 模组的品质、可靠性和长期功能性:

- 主板基材处理

- 首先要让零件可以牢牢地焊在电路板上,就得先处理基材的表面。这道工序往往由PCB厂先进行处理,接着才交给封装制造商。通常会包含清洁、粗化表面,以及涂上薄薄的一层金属 (通常是铜) 来增加导电性。

- 接着,会在处理好的基材上放上「钢网」。钢网是一种金属薄片,上面用雷射切割出跟电子零件大小位置相符的孔洞。

- 最后的印刷,会使用一种黏稠状的「锡膏」,里面含有细小的焊锡粉末。透过钢网的孔洞,锡膏会被挤压在电路板指定的位置,形成用来焊接零件的焊盘。

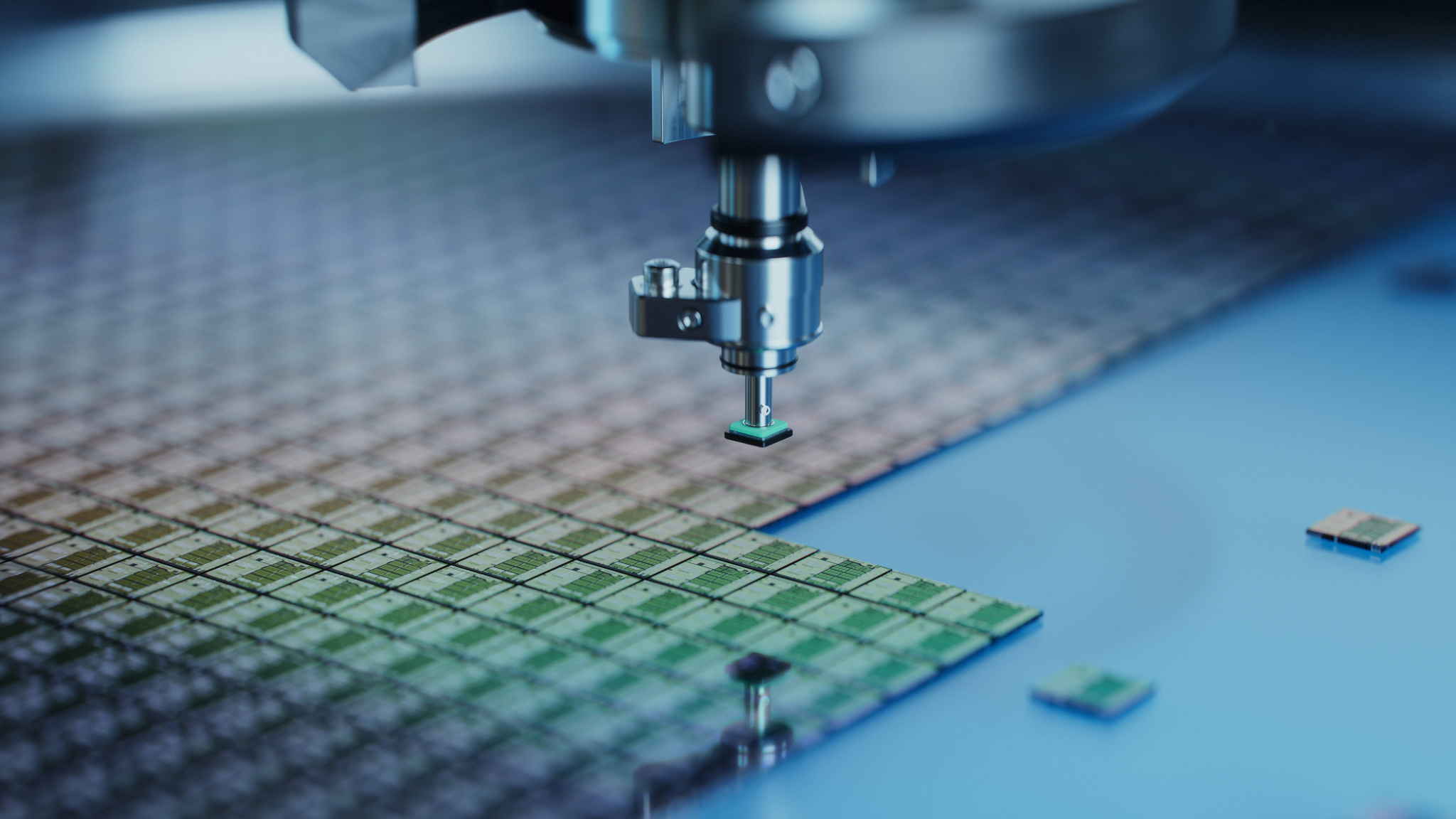

- 高密度表面黏着技术 (HD-SMT)

将锡膏印刷在电路基板的表面之后,接着就是将电子元件的焊脚置放在有锡膏的位置,于此阶段就会使用到有装载吸附喷嘴和视觉系统的「高速贴片机」。高速贴片机可以从供料盘或卷轴中个别抓取电子零件,然后非常精准地放在基板上。这个步骤的精准度非常重要,因为任何一点点的偏移都可能造成电路连接不良。之后,运用高温让锡膏融化,将电子元件焊接在电路基板上。

深入了解更多:系统级封装 - 高密度打件能力

深入了解更多:系统级封装 - 高密度打件能力

- 元件连结:固晶与打线接合

若要运用在更高阶的微小化产品,让这些电路板上的零件彼此「沟通」,就得靠另外两种技术:固晶技术 (Die Bonding) 和打线接合 (Wire Bonding)。首先是固晶技术,这个步骤就像盖房子打地基一样重要,这时会在基材上涂上极少量的导电胶,就像水泥一样把地基固定住。然后,再用非常精密的技术把没有外壳的整合电路 (IC),也就是「裸晶 (die)」放到定位好的基材上,接着施加高温高压,让晶片牢牢地黏在基板上,形成稳固可靠的连接。

另外一种打线接合,则是采用微米等级的金属线 (通常是铜线、金线或铝线),并透过焊针或球形接合技术,小心翼翼地将这些金属线焊接到事先规划好的焊盘上,达成电路互通。打线接合的优点是灵活度高,可以应付不同高度的零件,在电路板设计上更有弹性。

另外一种打线接合,则是采用微米等级的金属线 (通常是铜线、金线或铝线),并透过焊针或球形接合技术,小心翼翼地将这些金属线焊接到事先规划好的焊盘上,达成电路互通。打线接合的优点是灵活度高,可以应付不同高度的零件,在电路板设计上更有弹性。

- 封装阶段

在电气连接形成后,整颗 SiP 模组将用保护材料(通常是环氧树脂)封装。这一作法可以保护精密元件免受环境因素(如湿气、灰尘和物理冲击)的影响。针对不同需求取向可以采用不同的封装技术,除了全体封装(覆盖整个 SiP模组)外,还可以进行选择性和阶梯式封装。

深入了解更多:系统级封装 - 塑封能力、系统级封装 - 屏蔽能力

深入了解更多:系统级封装 - 塑封能力、系统级封装 - 屏蔽能力

- 测试与检验

封装完成后,SiP模组会进行严格的测试,确保功能和效能的正常运作。一般会包含电气测试,检查连线和零件有没有问题,也会用光学检测和 X光检测来看封装材料里面有没有瑕疵或空洞。功能测试的部分会模拟实际使用环境,来评估 SiP 模组整体的性能表现。

系统级封装SiP的优势

SiP 技术有许多可取之处:

- 尺寸轻薄:可以把很多零件整合在一起,让电子设备整个变得非常小巧。这对于消费性产品来说非常棒,例如穿戴式装置和智慧型手机。

- 效能提升:它能够缩短零件之间的电气路径,让讯号传输更快、讯号完整性更好,整台设备的效能也就跟着提升。

- 更可靠耐用:系统级封装技术可以保护零件免受外力、潮湿、灰尘等外来物影响,让电子设备更加稳定可靠。

- 快速上市:透过模组化设计,可以同时开发多种产品,并且缩短产品上市的时间。使得品牌客户,也就是客户们可以更快抢攻市场商机。

除了SiP,还有哪些微小化解决方案?

系统集成封装(SiP)技术是改变电子行业实现复杂功能的微小化和系统整合的解决方案之一。但是对于客户、产品甚至预算而言,要选择哪个解决方案可能存在多样性。因此,让我们来看看其他两种目前市场上讨论度极高的封装解决方案:

环旭电子技术探索篇|微小化技术本质:SoC、Chiplet、SiP

SoC (System on Chip) 系统单晶片

SoC 指的是将各种功能整合到单一晶片上,包含像是处理器、记忆体单元和输入/输出介面等重要元件。这种把功能集中在统一平台的做法简化了整体系统的架构,提升效率并缩小体积。尽管 SoC 技术仍被主流市场采用,但面对不断变化的功能需求势必要整合更多新的功能,面对这个问题,SoC技术已经开始出现制程上的瓶颈。

系统单晶片SoC 会面临什么挑战吗?

现今SoC所面临最主要的困难是它僵化的制造特性,限制了晶片因应动态需求的灵活性。虽然 SoC 技术能够整合不同功能,但却仅限于相同制程技术下的元件。这种缺乏弹性往往需要在进行修改或升级时,投入大量重新设计的功夫,进而导致开发时间延长和成本增加。这些挑战凸显了其他微小化技术的特性,例如小晶片模组(Chiplet)和系统级封装 (SiP)。

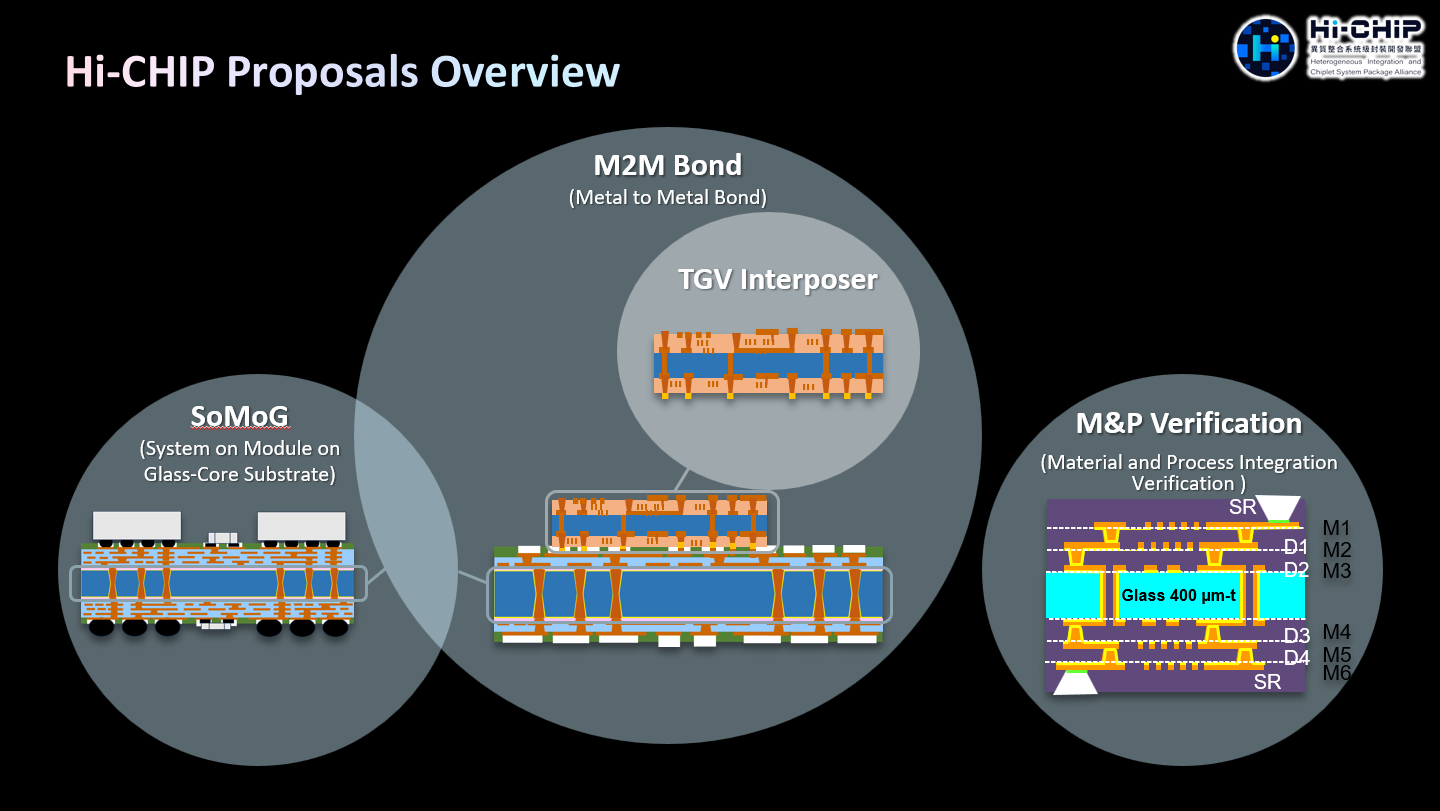

Chiplet 小晶片模组

近年来全球人工智慧 (AI) 应用蓬勃发展,对于高运算力及影像处理模组的需求也急遽增加,而Chiplet技术俨然成为 AI 晶片的首选方案。相较于SoC的封装方式,它的特色在于能够提供更大的弹性,因为SoC所有元件都必须采用相同的制程,但Chiplet技术可将采用不同制程的元件整合于一个基板上。这种弹性不仅能提升客制化能力,使得Chiplet技术成为高效运算、AI领域的绝佳选项。

小晶片模组Chiplet会面临什么挑战吗?

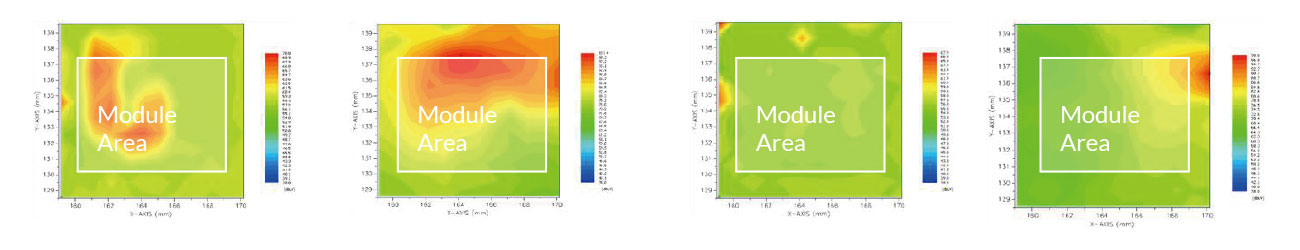

该种制程最主要问题会是在于生产良率与成本,因为要能够多颗IC组装于基板上的复杂制程需要极度精密的技术,这相对会提高缺陷率,进而促使成本飙升。此外,如何在紧凑的封装空间内管理多颗IC的散热与电力分配也是另一道难题,因为功率密度的提升可能会加剧散热问题,进而影响整体系统的稳定性。尽管面临各种挑战,但是封装技术正持续研发解决方案,为Chiplet技术在 AI、高效运算等更多领域打造更加坚实的基础。

产业中有各种先进的封装解决方案可供选择,如何选择皆取决于产品的性能要求。虽然每个解决方案都有其独特的优势,但 SiP 在许多应用中脱颖而出。它在微小化、功能性和成本之间取得了卓越的平衡。当进行综合评量时,SiP其成熟、灵活极具成本效益的解决方案,着实适用于各种应用领域。

跟紧产业脉动

随时掌握第一手产业创新科技、应用与深度新闻

订阅 USI 博客

随时掌握第一手产业创新科技、应用与深度新闻