-

05/07/2026

05/07/2026

製程幕後|從「製造」走向「創造」Ep.1:揭秘 USI技術先行軍

作為全球領先的電子製造服務商,USI 環旭電子透過技術核心「全球營運發展總處」(Corporate Operations Development,以下稱COD),正帶領企業實現從 0 到 1 的技術跨越 。本系列將由環旭電子COD團隊的李訓發副總 (以下稱Jona)及其麾下的技術專家來為我們解析,如何透過深度解構與技術韌性,突破業界最難的 Chip 008004 與 2mil(密耳)間距 關卡 。 了解更多 -

12/31/2025

12/31/2025

突破 AI 能源高牆:Power Block 與 3D 微小化解決方案

近期在 IMPACT 2025 研討會上,USI 環旭電子的沈里正博士受邀擔任主題講者,分享了針對高效能運算(HPC)的技術實踐路徑 。面對 AI 伺服器對算力的渴求,我們認為「電力傳輸 (Power Delivery)」已不再是配角,而是決定 AI 發展速度的關鍵燃料 。 了解更多 -

12/15/2025

12/15/2025

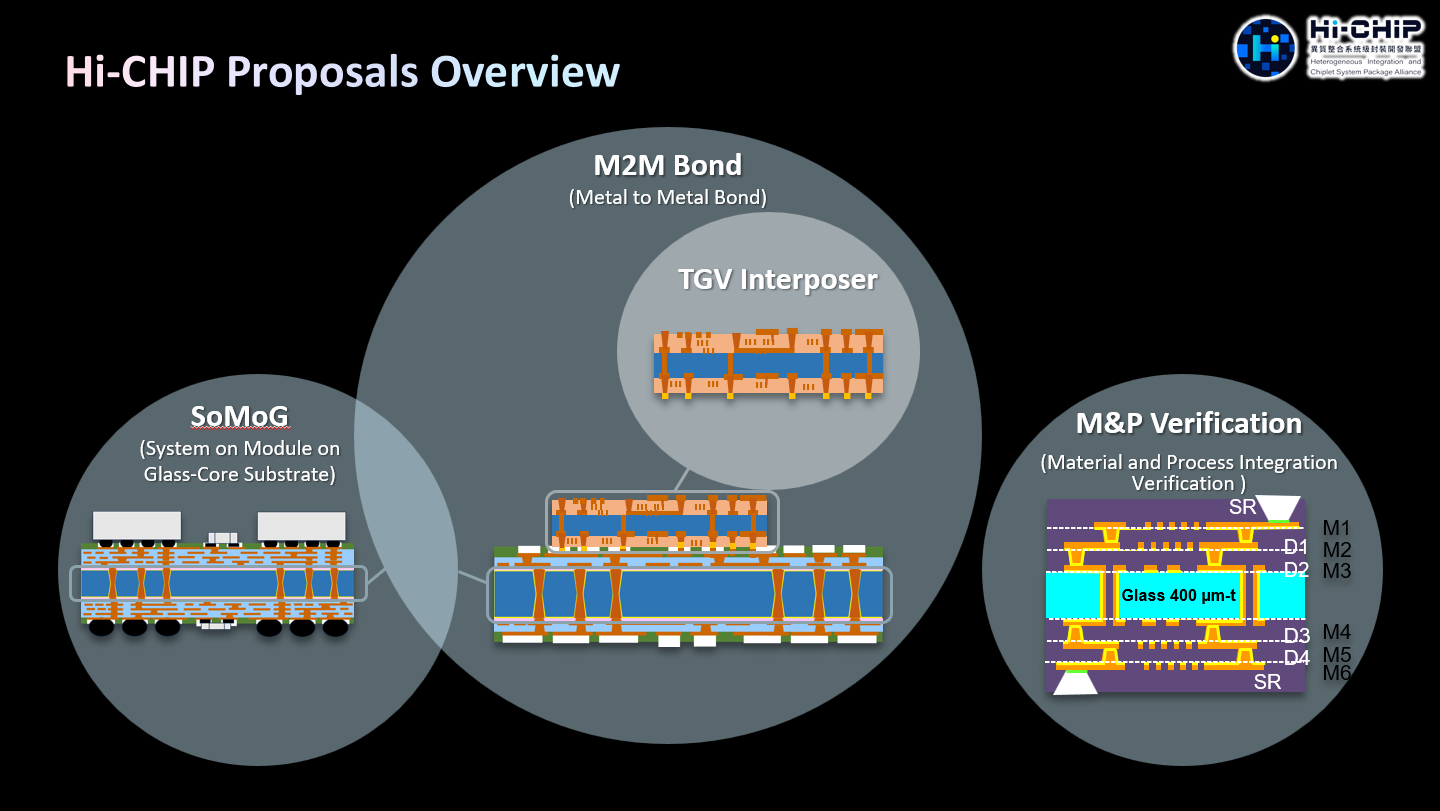

駕馭車用 HPC:探尋玻璃基板系統模組(SoMoG) 技術的「最佳甜蜜點」

今年(2025),環電的沈里正博士受邀擔任IMPACT 2025 研討會主題講者,在會議期間,沈博士亦代表 Hi-CHIP 聯盟(該聯盟包含欣興電子 Unimicron 及工研院 ITRI 等產業關鍵腳色),發表了題為「玻璃核心基板上的系統模組 (SoMoG)」的主題演講,直指汽車產業的關鍵轉折點。 了解更多 -

10/21/2025

10/21/2025

【研發超展開】數位類比轉換器(DAC)控制偏壓電流創新解決方案,智慧電源的關鍵突破

環旭電子的開發團隊提出全新的 「數位類比轉換器(DAC) 控制電源轉換晶片偏壓電流解決方案」。這項創新技術不僅解決了精度、穩定性與靈活度的問題,更帶來了自動化與遠端控制的能力,為新世代電子系統提供了更高的設計自由度與可靠性。 了解更多 -

09/11/2025

09/11/2025

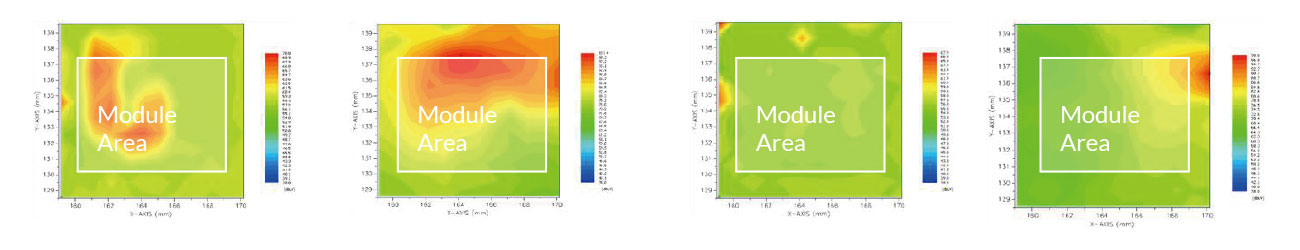

從「經驗」到「精準」:如何用AI智慧演算法,實現高效射頻預測模型

在電子製造產業中,每一個微小的環節都可能決定產品的最終性能與良率。射頻(RF)電路設計的效能,直接決定了無線通訊設備的性能優劣。其中,「阻抗匹配(Impedance Matching)」作為確保訊號完整性與功率傳輸效率的關鍵環節,長期以來都是一項極具挑戰性的任務。 了解更多 -

08/15/2025

08/15/2025

活動|DIGITIMES 2025 MCU 論壇 – USI 談異質整合驅動 MCU 應用新格局

在2025年8月8日,這個別具意義的父親節,一場關乎未來智慧控制核心的思辨,於DIGITIMES所舉辦的【智控未來,MCU再進化】微控制器論壇中熱烈展開,該活動匯集許多系統整合領域的代表性企業如德州儀器、恩智浦、瑞薩電子及工研院等。當產業目光聚焦於MCU本身的算力與功能提升時,USI環鴻科技技術長方永城 (John Fang) 以「異質整合驅動MCU應用新格局」為題,提出一個顛覆性的觀點 了解更多 -

07/16/2025

07/16/2025

系統級封裝(SiP)屏蔽格柵技術:細如髮絲的技術水準

延續上一篇的「共形屏蔽」技術,本文將繼續說明「分段型屏蔽」,USI環旭電子是如何透過特殊開發的分段型屏蔽(Trenching & Filling epoxy) 以及屏蔽格柵 (Shielding Fence)等兩大手法,為客戶客製化微小化產品,達成細如髮絲之間的工藝水準。 了解更多 -

06/20/2025

06/20/2025

活動|【寬能隙半導體技術論壇】為AI巨獸打造強力心臟:模組化與微小化如何革新伺服器電源效率

在6月12日當天,受到產業媒體夥伴「新電子」的邀請,我們的方技術長有幸前往擔任「寬能隙半導體技術趨勢暨產業應用高峰論壇」的主講者之一,向產業界的各位先進分享關於AI領域的技術發展,特別是電源供應的議題。 了解更多 -

06/09/2025

06/09/2025

FEDS:無線射頻自動化開發的關鍵引擎

延續FEDS平台在前兩篇文章中所展現的效益:「電路佈局審查」、「電源完整性模擬的自動化」,本文將再繼續深入探討FEDS系統在射頻設計領域所貢獻的自動化開發應用,以及如何協助工程師克服複雜性、提升效率。 了解更多

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞