搜尋

- 07/11/2022

【微小精確、事半功倍】Ep.2 站穩微小化的競爭能力

過去,半導體IC元件和晶片的封裝大多採用標準的IC封裝技術,如單芯片BGA(球柵陣列)封裝。但為了回應5G、物聯網、自動駕駛汽車、智慧城市、遠端醫療等應用的需求,這些傳統的IC元件封裝技術已經無法完全滿足當今的高速計算和傳輸需求。

正因為如此,如雙面塑封和扇入/扇出此類的先進的系統級封裝(SiP)製程,已經成為資通訊產品市場不可或缺的技術。半導體領先大廠如台積電、英特爾、三星……等,均在加速部署先進封裝技術,未來如何在技術上取得突破、實現成本和性能的平衡,已成為產業最重要的發展戰略之一。

有鑑於此發展趨勢,自2008年起,環旭電子已開始投入系統級封裝製程技術,例如高密度貼片(High-Density SMT)、塑封(Molding)及遮罩(Shielding)技術。

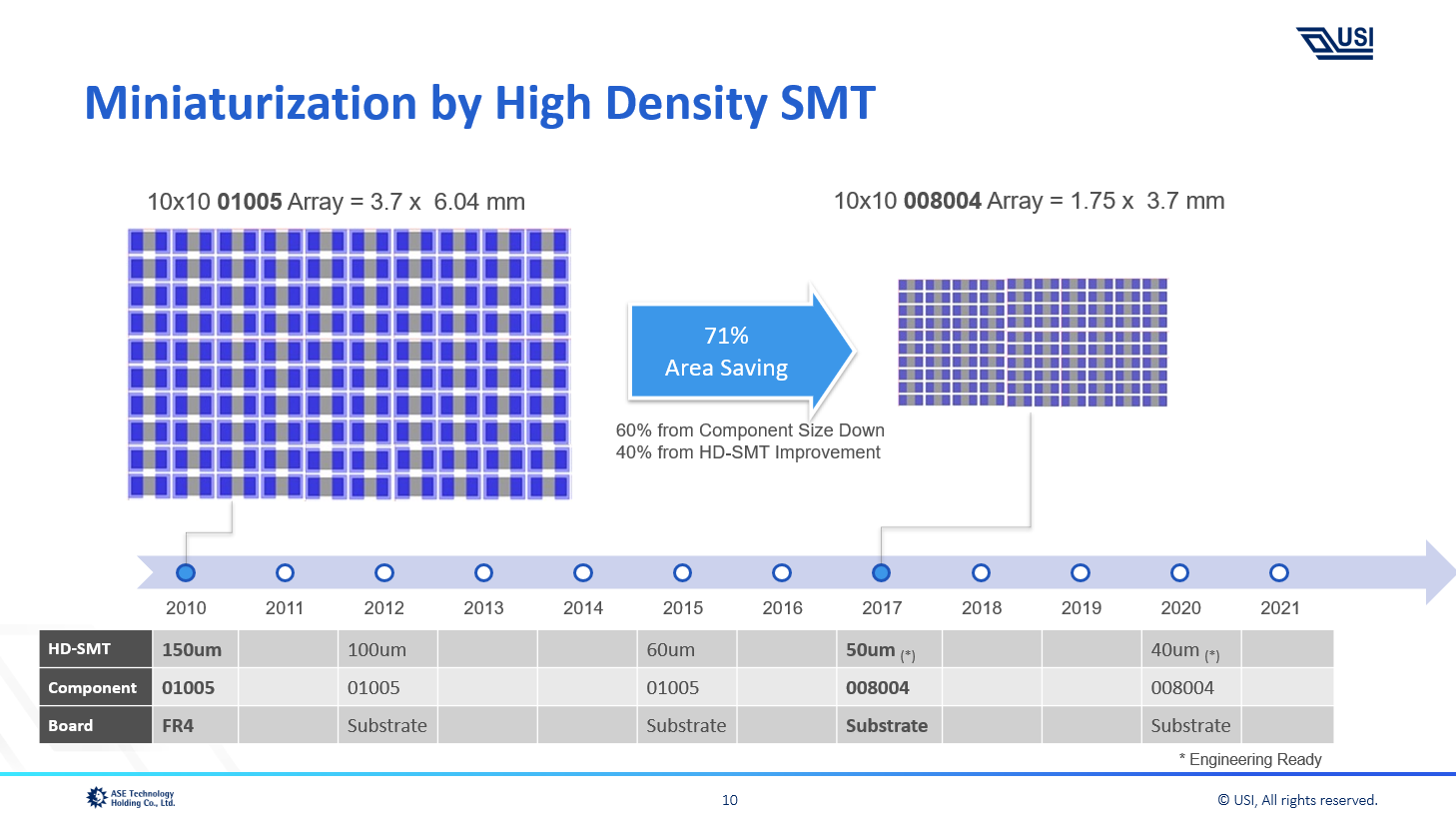

高密度貼片技術

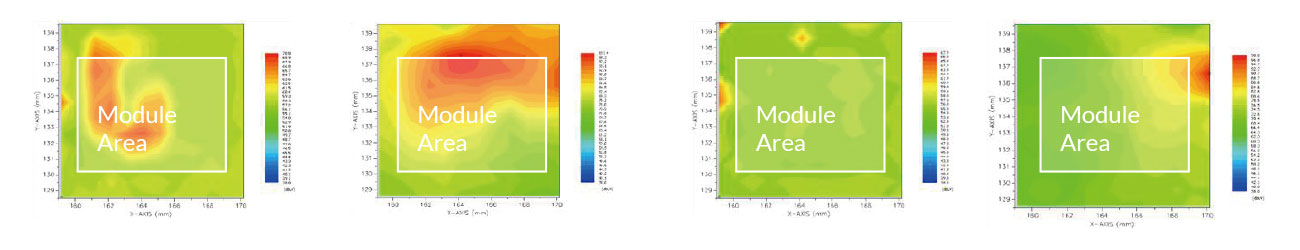

在設計中零組件的數量多寡及排布間距,即是影響模組尺寸的最主要關鍵。在貼片製程方面,業界普遍元件間距為150μm以上,環旭電子已達到小於成人髮絲直徑的50μm,顯現出環旭電子在貼片工藝的超高精準度。以10x10陣列做比較,大幅縮減超過70%的基板尺寸,其中的40%乃源自於貼片技術的突破。

深入了解更多:系統級封裝 - 高密度貼裝能力

塑封與遮罩技術

與傳統的板階組裝相比,塑封技術是先進封裝技術的一個關鍵分水嶺,它可以有效地保護高密度封裝中的微距元件,從而使得空間效率最大化。

由於高密度貼片採用的是微小化零組件,因此組件與載板之間的連結,吃錫量大幅減少。為提高貼片可靠度及阻抗性,避免外界濕度、高溫及壓力等影響,塑封製程可將完整的零組件密封包覆在載板上。以高集成的系統級封裝來說,一般委外封測(OSAT)集成約100顆左右,而環旭電子目前的技術可容納高達900顆組件。

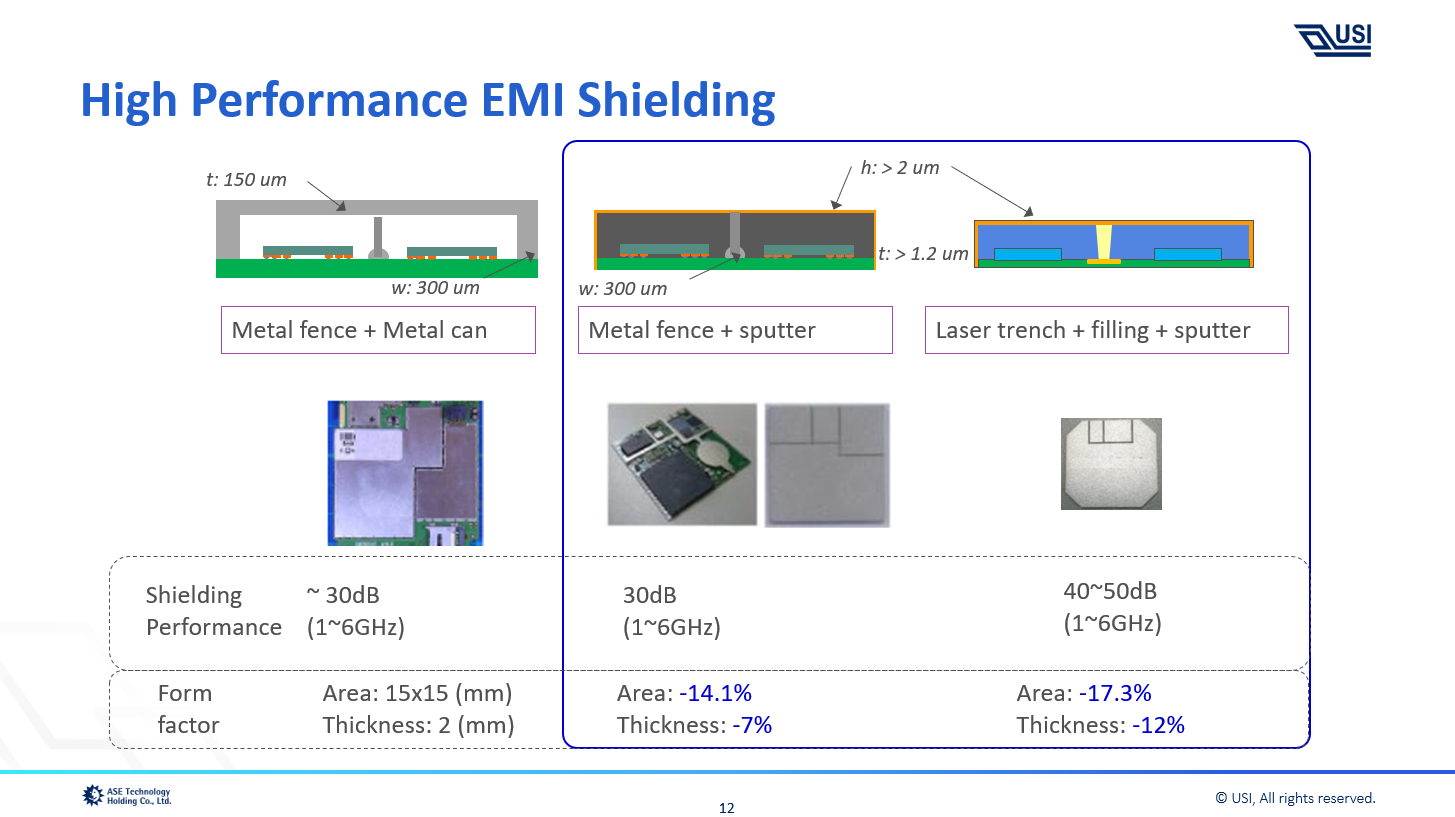

另一方面,要將上百顆電子元件塑封,則需要遮罩來隔離電子元件間的訊號,避免互相干擾。環旭電子所開發的共形、分段型遮罩皆可達到小於2μm,為其他元件騰出超過17%的空間,並可遮罩40-50 dB的電磁干擾。

對於寸土寸金的微小化模組來說,減少150μm的厚度是一大進步。此外,塑封和元件之間的頂部和側面空間也可以再減少,進一步降低厚度與縮小面積。

深入了解更多:系統級封裝 - 塑封能力、系統級封裝 - 遮罩能力

站穩微小化世界的競爭力

隨著時代演進,科技產品更加強調輕便型與功能性的結合,因此產品所能使用的空間更是寸土寸金,透過系統級封裝制程,整體可節省約30-40%的板面積,憑藉著微型化及模組化的異質整合優勢,板端、天線及機構的設計整合上更加有彈性,這是IC製程所做不到的。

先進封裝技術的突破正在影響產業供應鏈、改變競爭格局,面對微小化時代的來臨,微小化技術已然成為不可或缺的競爭力。環旭電子從WiFi產品就開始進行佈局、站穩腳步,憑藉多年積累在射頻、穿戴式裝置等產品的豐富制程經驗,以及持續突破的技術,準備迎接這一場全球關注的「毫釐之爭」。

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞