搜尋

- 11/14/2024

FEDS:百倍效率革命!打造自動化電路審查高效流程

在傳統PCB開發歷程中,往往為了符合開發時程表的期程,我們發現Layout工程師及各個功能開發團隊,時常被要求必須在一周內完整解決檢查報告中的每一項違規點。檢查報告中的違規點數量,以單顆CPU為例,約有三、四千個,雙CPU則經常多達七、八千個。由此可見,這一項要求的背後,需要的是硬體及電源開發工程師即時審查及修正。同時,也必須要有4至5名Layout工程師每天熬夜趕工,以手動進行細部修正所有的違規項目。

傳統PCB審查歷程的四大痛點

在時間極度壓縮的情況下,如何提升效率、增加處理時間,成為了第一要務。因此,環旭電子CE 研發團隊在累積的開發案中歸納出四大關鍵痛點,其中又以第一點最為重要。

- 如何提升修正Layout違規點的效率,並加快進入出圖生產(Gerber Out)的過程?

- 如何整合來自不同來源的檢查需求,減少工程師的彙整負擔?

- 如何統一各功能的檢查標準,避免人為標準的落差?

- 如何記憶各項檢查項目及規範細節,降低工程師每次執行檢查的作業量?

解決方案 - 什麼是前端設計與模擬自動化平台(FEDS)?

前端設計與模擬自動化平台 (FEDS) 是一套由USI環旭電子自主開發,專為提升電子產品設計效率與品質而生的工具平台。它的核心概念是將設計過程中許多重複性高、易出錯的任務自動化。從一開始的物料清單生成與檢查,到後續的電路圖、PCB佈局檢查,甚至是複雜的電磁模擬,它都能提供全方位的自動化支援。不僅能大幅縮短產品開發週期,更能有效降低人為錯誤的發生機率。

你可以將FEDS想像成Google平台,此平台不僅提供電路佈局審查功能,同時,它也擁有非常多樣的延伸應用工具,例如:原物料清單(BOM)生成與檢查、線路圖檢查 (Schematic Check)、模擬仿真電性特性(RF \PI Simulation)符合電性規定、RF線上協同作業(RF Matching) 包含:優化RF特性、RF測試自動化、RF測試模擬結果比對…等等。

自動化平台 (FEDS) 最大的差異化優勢,就在於極度靈活的客製化能力。傳統的商業化EDA工具往往功能過於通用,而FEDS允許企業根據自身產品特性與設計流程,自行開發並整合各種檢查規則與模擬工具,能夠更精準地滿足企業的需求,提升設計效率。

自動化電路佈局審查

PCB開發工程師在進行電路佈局審查時最需要的需求主要有四項:

- 常被用於檢查CPU訊號介面是否符合其規範的第三方工具。

- 不同平台設計指南(PDG)對各個訊號介面的規範要求。

- 公司內部各研發單位或製造部門的設計經驗與需求。

- 戶研發工程師對產品的特殊檢查需求。

上述需求都被整合在自動化電路佈局審查工具中,它具備不斷擴充功能,可建立新檢查項目並幫助工程師即時修正佈線。自動檢測完成後,可輸出報告供研發工程師檢視。此外,系統會收集檢測數據以進行統計分析和設計檢討。

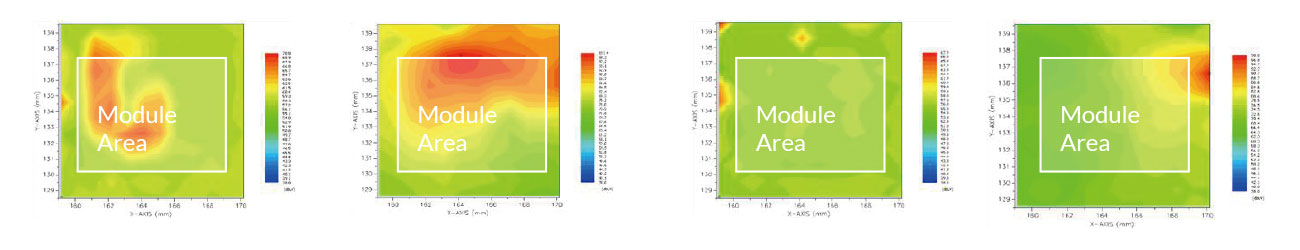

目前自動化電路佈局審查工具有五大類,包括Routing Check, Pad and Placement及Via Check等。此外,自動化電路佈局審查可針對產品的特殊需求,開發專利檢查項目,如:差動訊號出線對稱性檢查、避免串擾效應的檢查,以及電源完整性優化的接地過孔密度檢查。

1) 差動訊號出線對稱性檢查:確保差動訊號在焊墊及通孔出線時的走線對稱。

2) 避免串擾(CrossTalk)效應:確保差動訊號的焊墊及通孔之間不被其他訊號穿越,以減少干擾。

3) 接地過孔密度檢查:此功能可在Layout工程師初步完成走線時,快速檢查電源網路(PDN),提前解決電源完整性問題,大幅節省時間和資源。

導入成效

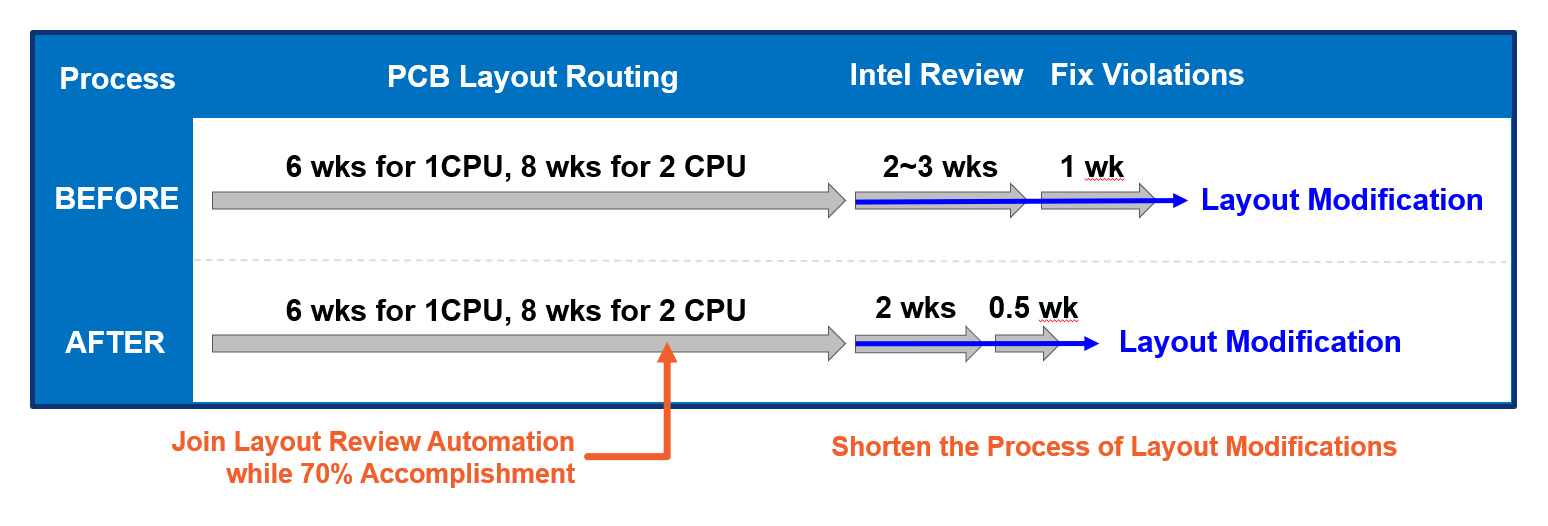

圖1. 透過自動化審查工具,PCB Layout開發時程的優化比較

自動化電路佈局審查工具主要可以在電路圖完成70%的佈線之前,自動找出違規並修正,在整體開發過程中,可顯著發現兩大項的優化成長:

1. 查找Board file上違規點的正確性與一致性

• 導入前: 倚賴經驗豐富工程師,意見不一,耗時且效率低。

• 導入後: 自動化檢查,統一標準,縮短檢查及修正違規點的總時數。

2. 自動化檢查與人工檢查效率比較

• 導入前: 人工檢查耗時長,尤其是大型專案。

• 導入後: 自動化檢查速度快,大幅提升效率,可降低工程師所需的重複性工作。

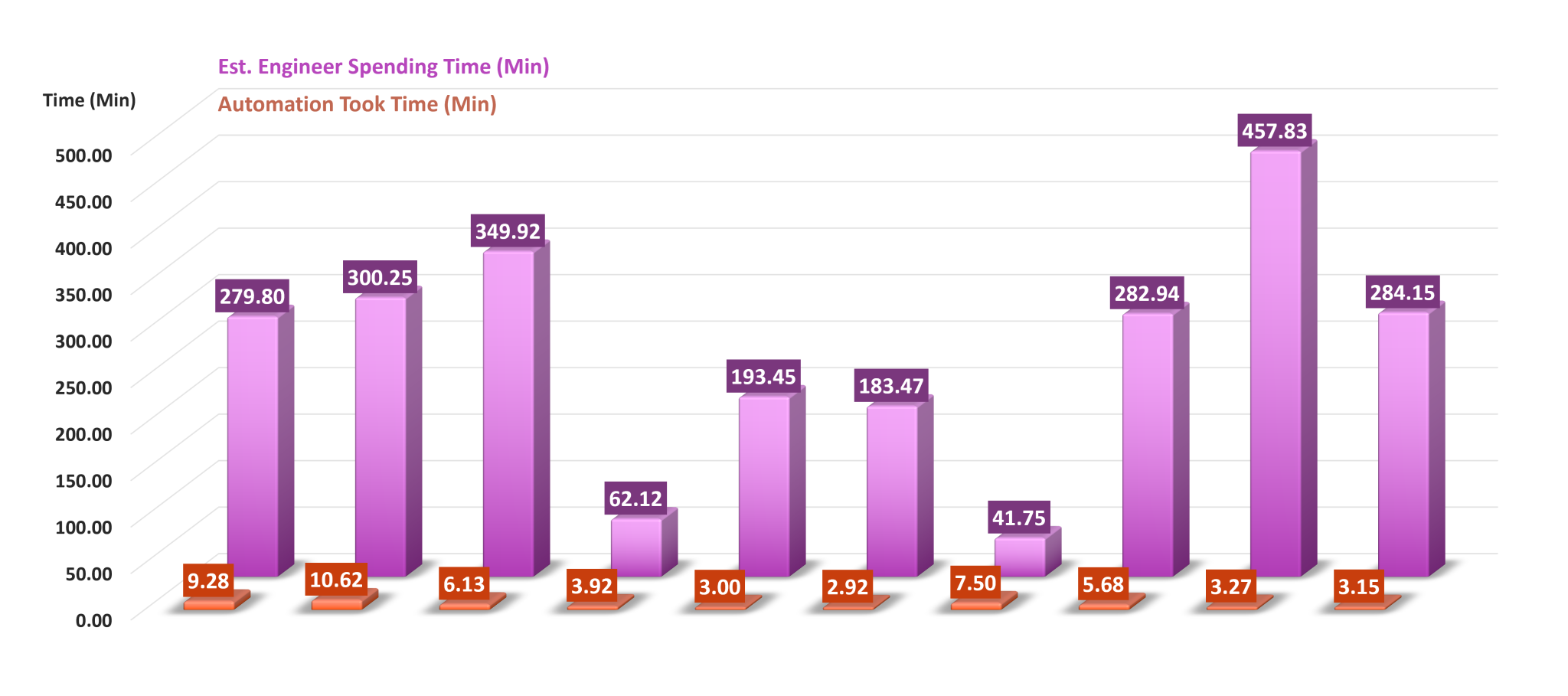

從2023年的Layout專案加以分析、比較自動化與人工檢查的工時,圖2明顯可看出兩者的差距已超過十倍,甚至是百倍以上,由此可知自動化對於布局審查作業,有顯著提高效率的貢獻。

圖2. 人工檢查與自動化檢查的耗時比較

綜上所述,自動化檢測系統的導入,為企業帶來了多方面的效益:

- 大幅加速產品開發效率: 縮短Layout檢查時間,加速產品上市時程。

- 提升檢查結果的一致性與可靠性: 降低人為因素造成的錯誤。

- 自動化平台的靈活性:能針對不同產品、不同製程,客製化開發所需的檢查項目。

- 提高產品品質:及早發現並解決設計問題,降低產品瑕疵率。

展望未來,隨著產品設計的複雜度將持續增加,對Layout檢查的要求也將越來越高。透過自動化系統,企業能將工程師從繁瑣的重複性工作中解放出來,使其能夠專注於更具創新性的工作,提升效率、優化品質。「前端設計與模擬自動化平台」已然是環旭電子開發服務中不可或缺的一環。

隨時掌握第一手產業創新科技、應用與深度新聞