搜尋

- 08/15/2025

活動|DIGITIMES 2025 MCU 論壇 – USI 談異質整合驅動 MCU 應用新格局

主講者:方永城 John Fang, Ph.D., 環鴻科技技術長暨資深副總

在2025年8月8日,這個別具意義的父親節,一場關乎未來智慧控制核心的思辨,於DIGITIMES所舉辦的【智控未來,MCU再進化】微控制器論壇中熱烈展開,該活動匯集許多系統整合領域的代表性企業如德州儀器、恩智浦、瑞薩電子及工研院等。當產業目光聚焦於MCU本身的算力與功能提升時,USI環鴻科技技術長方永城 (John Fang) 以「異質整合驅動MCU應用新格局」為題,提出一個顛覆性的觀點:MCU的下一步進化,戰場已不在晶片本身,而在於如何「封裝一個系統(Packaging a System)」。這場演說,不僅展示了系統級封裝(SiP)技術的巨大潛力,更為AIoT與智慧邊緣應用的未來,描繪出一幅清晰且可行的藍圖。

後摩爾定律時代的必然:從晶片思維到系統整合

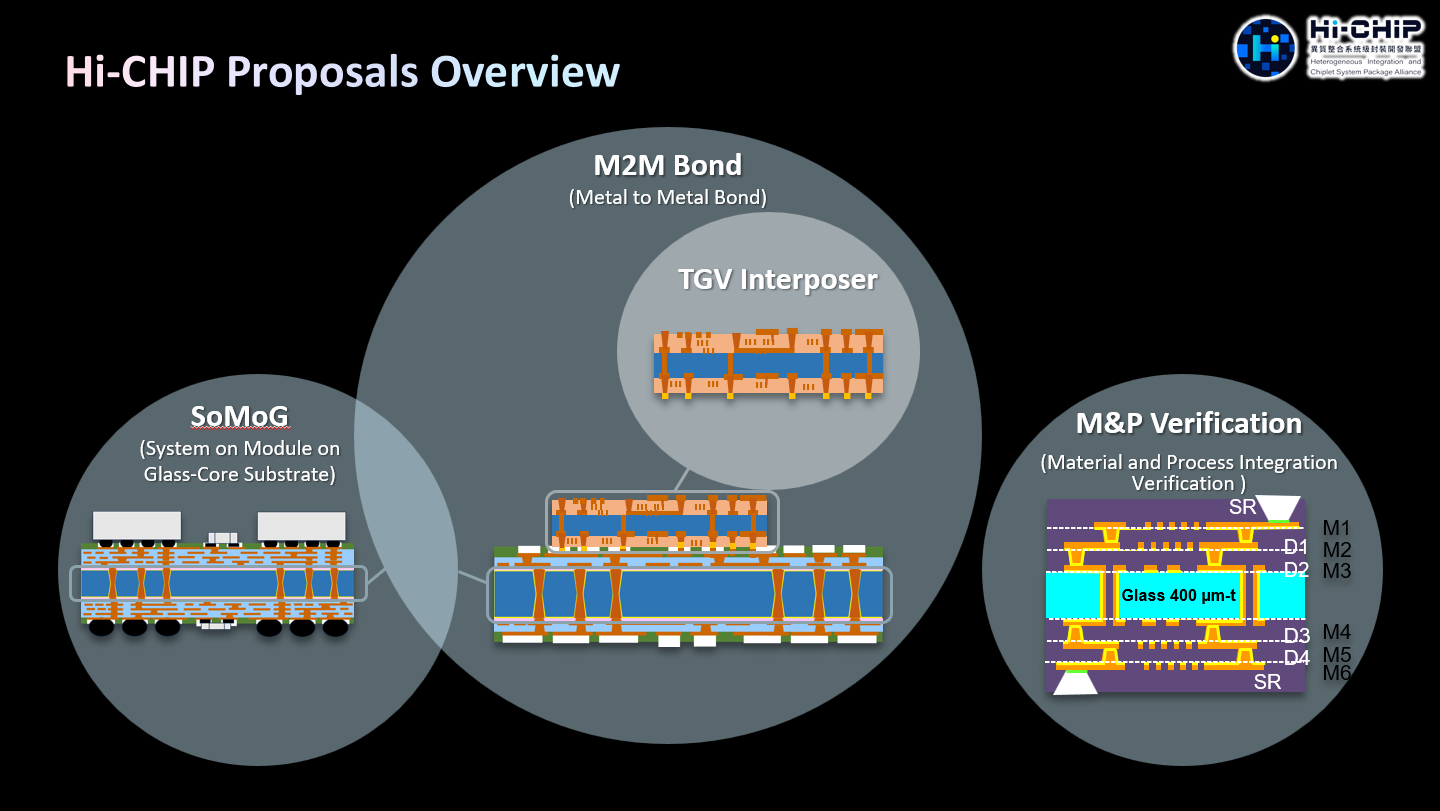

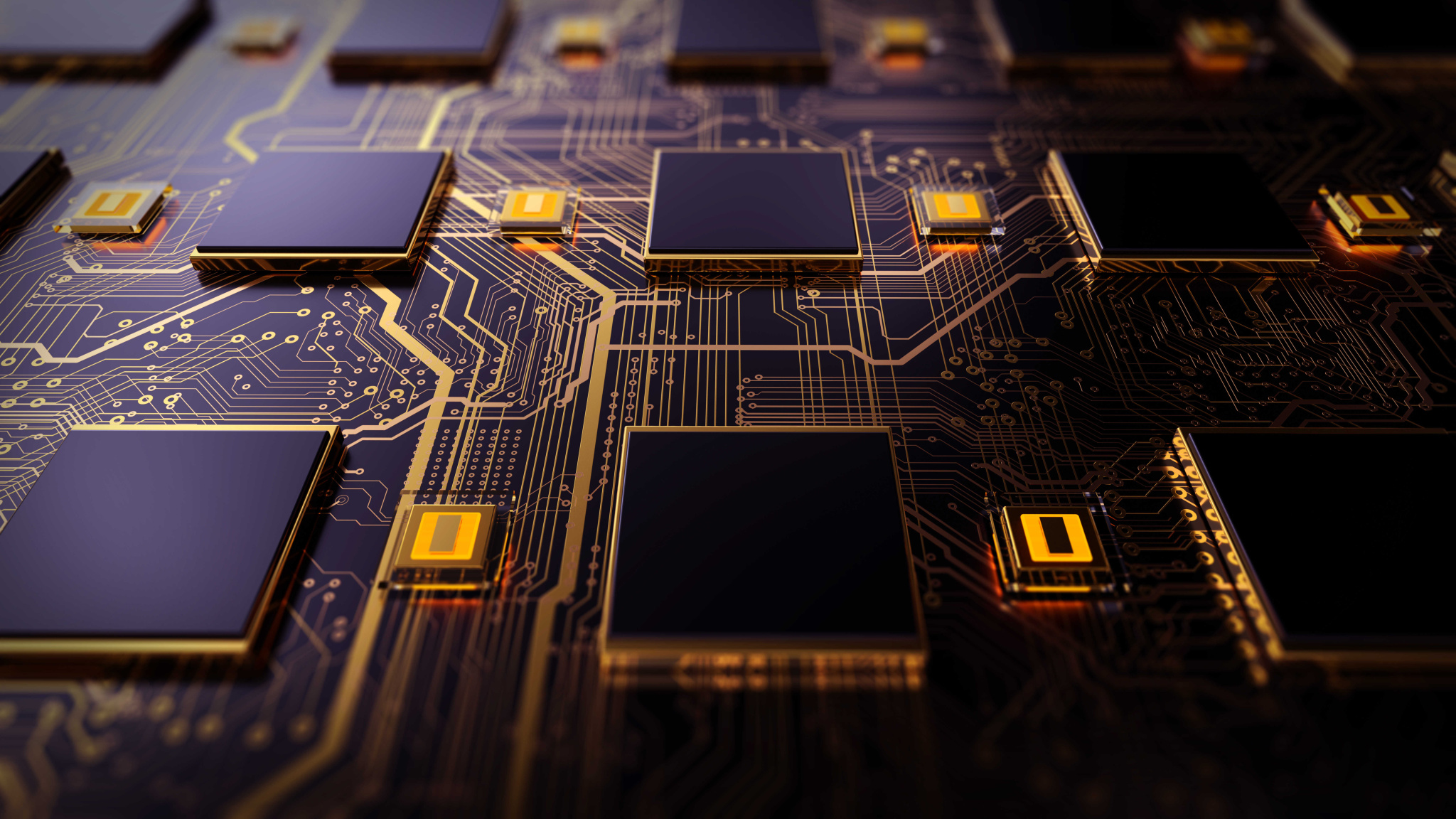

在論壇的開場,方技術長隨即開宗明義地指出,隨著摩爾定律趨緩,單純追求晶片製程微縮的道路已日益艱難。傳統上,工程師在系統級晶片(SoC)與系統單板(SoB)之間做選擇,前者整合度高但開發成本與週期驚人,後者雖靈活卻犧牲了體積與功耗。他接著強調,系統級封裝(SiP)技術正是在此背景下應運而生的最佳解方,它透過先進的封裝技術,將MCU、記憶體、感測器、電源管理晶片,甚至天線等不同製程、不同材質的「小晶片(Chiplet)」與被動元件,整合在一個高度緊湊的封裝體內。

圖說:USI環鴻科技技術長方永城 (John Fang)應邀成為MCU 論壇演講嘉賓。

「我們觀察到一個很明顯的趨勢,就是上游的封裝測試廠想往下游走,而我們這些比較下游的系統廠則想往上游走,大家最終會碰在一起。」技術長在演講中生動地描述了產業的動態。他坦言,許多傳統OSAT同業也開始投入SiP領域,而環鴻科技最大的差異化優勢,則在於其深厚的「系統設計能力」。憑藉身為全球頂尖EMS/ODM廠的經驗,環鴻科技提供的SiP服務,遠不止於後段的封裝代工。「在前端的硬體、軟體設計,我們也都有能力可以處理」技術長自信地表示。這意味著環鴻科技能從客戶的應用場景出發,提供從晶片選用、電路設計、軟體驅動、系統驗證到最終量產的一站式解決方案,這正是單純的封裝廠難以企及的系統級價值。

「微小化」不只為輕薄,更為高效能與新應用

當談及SiP的核心效益,技術長首先聚焦於「微小化」。他以環鴻科技操刀的智慧手錶為例,透過將MCU、LPDDR2記憶體及76個被動元件整合,成功將功能電路面積從221mm²大幅縮減至81mm²,尺寸銳減63.4%。另一個極端的例子即是膠囊內視鏡,SiP技術將其內部複雜的電路極致壓縮,使膠囊尺寸得以縮小,直接提升了醫療體驗的舒適性。

應用實例列表

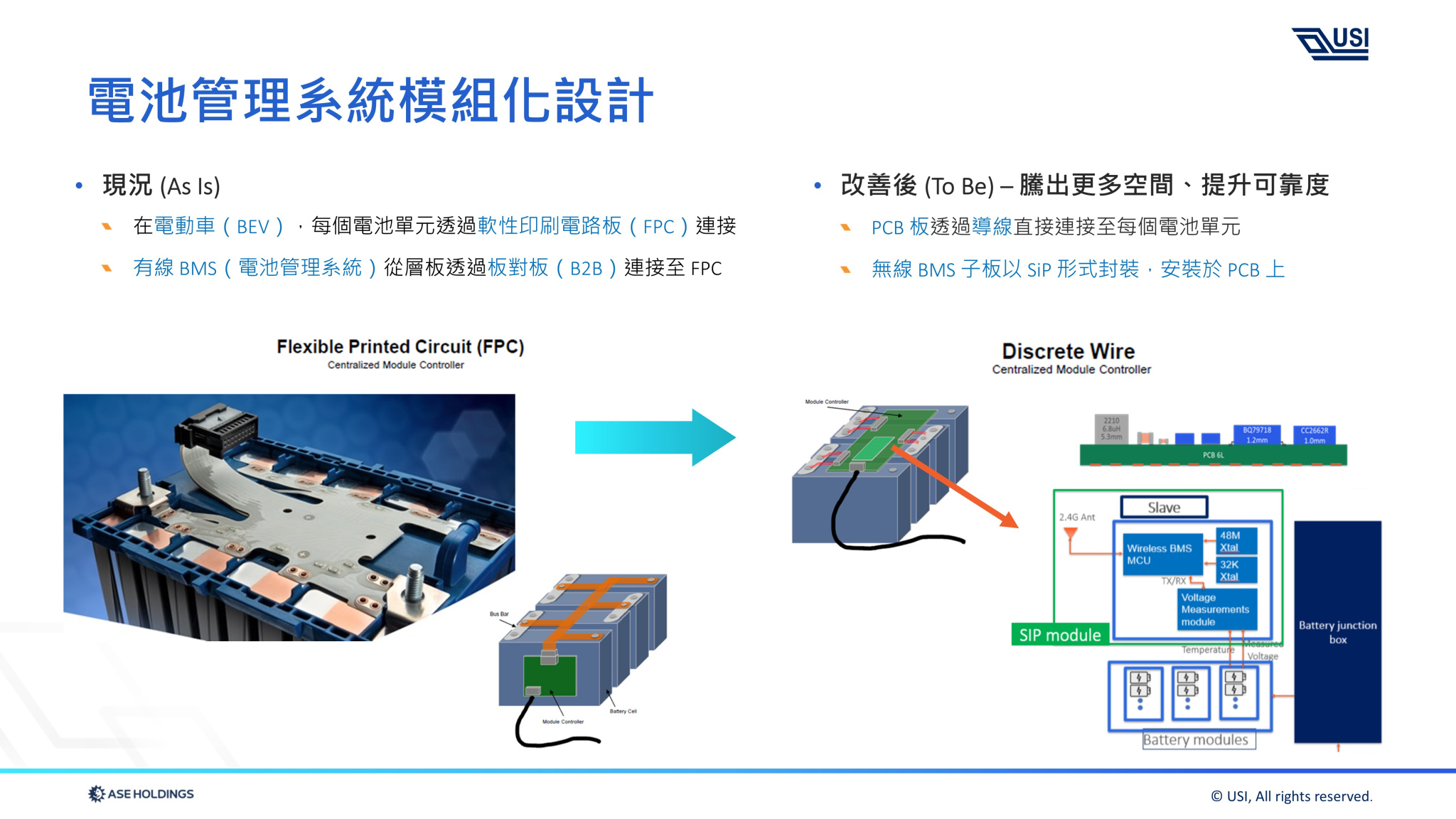

- 電動車電池管理系統(BMS):從傳統 FPC 連接架構,進化為無線 SiP 模組,提升可靠性並節省安裝空間。

- 醫療膠囊內視鏡:以 SiP 技術整合影像處理與無線傳輸功能,達到極致小型化。

- 混合式智慧手錶:尺寸縮小 63.4%,簡化主板設計,並保留全功能運作。

圖說:SiP技術讓膠囊內視鏡的微小化成為可能。

然而,微小化的意義遠不止於滿足消費性電子對「輕薄短小」的追求。方技術長分享了與AI客戶的合作經驗,揭示了微縮的另一層戰略意義。「大家想像一下,以前AI伺服器的板子那麼大,我們現在也要想辦法把它縮小。為什麼?因為要騰出空間來放Power(電源)。」他一語道破關鍵。

在AI算力需求呈指數級增長的今天,功耗與散熱已成為最大瓶頸。透過SiP將元件間的路徑縮到最短,不僅提升了訊號傳輸效能,更直接降低了整體功耗。「一個國家的算力,其實是受到它的電力影響。」方技術長指出,在AR/VR眼鏡、智慧手錶這類電池容量極其有限的裝置上,功耗的降低更是決定產品續航力與使用者體驗的生死線。SiP 不僅能透過先進製程減少漏電,還能在 PCB 設計層面縮短連接距離,達成整體性能與能源效率的雙重提升。

模組化賦能創新,加速產品上市進程

SiP的第二大支柱是「模組化」。透過將一個預先驗證過、功能完整的MCU系統封裝成標準化模組,客戶在開發新產品時,無需再為複雜的底層電路耗費心神。技術長以電動車的電池管理系統(BMS)為例,傳統方案需透過複雜的軟排線(FPC)連接,而環鴻科技則開發出無線BMS SiP模組,不僅可靠度更高,更為寸土寸金的電池包釋放出寶貴空間。另外,在複合式智慧腕錶的案例中,客戶的主機板設計被極大簡化,只需將SiP模組、機芯與震動馬達組裝即可,大幅降低了開發門檻與組裝難度。

圖說:將BMS模組化,不僅提升可靠度,更節省了電動車內部空間。

「Time to Market,這是最大的好處。」技術長總結道。一個預先通過認證的SiP模組,如同一個即插即用的樂高積木,能讓客戶專注於自身的核心應用與軟體開發,省去大量硬體驗證時間。這不僅保護了模組內的IP,更讓產品的迭代與創新速度呈倍數提升。最終,SiP模組方案能帶來約30%的厚度縮減、高達40%至60%的面積縮減,並能根據產品ID需求,客製化成任何「想像得到或想像不到的形狀」。簡而言之,系統級封裝 SiP的優勢,可以濃縮成三大面向:

- 模組化 — 簡化組裝流程,縮短開發時程(Time-to-Market),並強化知識產權保護。

- 微小化 — 提供更大設計自由度,讓系統整合更靈活。

- 商品化 — 厚度縮減達 30%,面積縮小 30%,並能因應不同場景需求打造客製形狀。

圖說:系統整合採用SiP的重點核心價值。

「系統整合能力」決定 MCU 的未來

在演講的尾聲,方技術長重申,環鴻科技提供的SiP模組是軟硬整合的完整系統,從底層的RTOS、Android/Linux驅動,到上層的雲端服務對接與各國法規認證,皆在環鴻科技的服務範疇。這場演講為「MCU再進化」的論壇主軸提供了最強而有力的註解,MCU的未來,將由系統整合能力定義。當智慧控制無所不在,環鴻科技正以「封裝系統」的獨特能力,扮演著那個為萬千智慧裝置賦能的關鍵「父親」角色,著實為產業的下一代發展奠定紮實基礎。

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞