搜寻

- 08/15/2025

活动|DIGITIMES 2025 MCU 论坛 – USI 谈异质整合驱动 MCU 应用新格局

主讲者:方永城 John Fang, Ph.D., 环鸿科技技术长暨资深副总

在2025年8月8日,这个别具意义的父亲节,一场关乎未来智慧控制核心的思辨,于DIGITIMES所举办的【智控未来,MCU再进化】微控制器论坛中热烈展开,该活动汇集许多系统整合领域的代表性企业如德州仪器、恩智浦、瑞萨电子及工研院等。当产业目光聚焦于MCU本身的算力与功能提升时,USI环鸿科技技术长方永城 (John Fang) 以「异质整合驱动MCU应用新格局」为题,提出一个颠覆性的观点:MCU的下一步进化,战场已不在晶片本身,而在于如何「封装一个系统(Packaging a System)」。这场演说,不仅展示了系统级封装(SiP)技术的巨大潜力,更为AIoT与智慧边缘应用的未来,描绘出一幅清晰且可行的蓝图。

后摩尔定律时代的必然:从晶片思维到系统整合

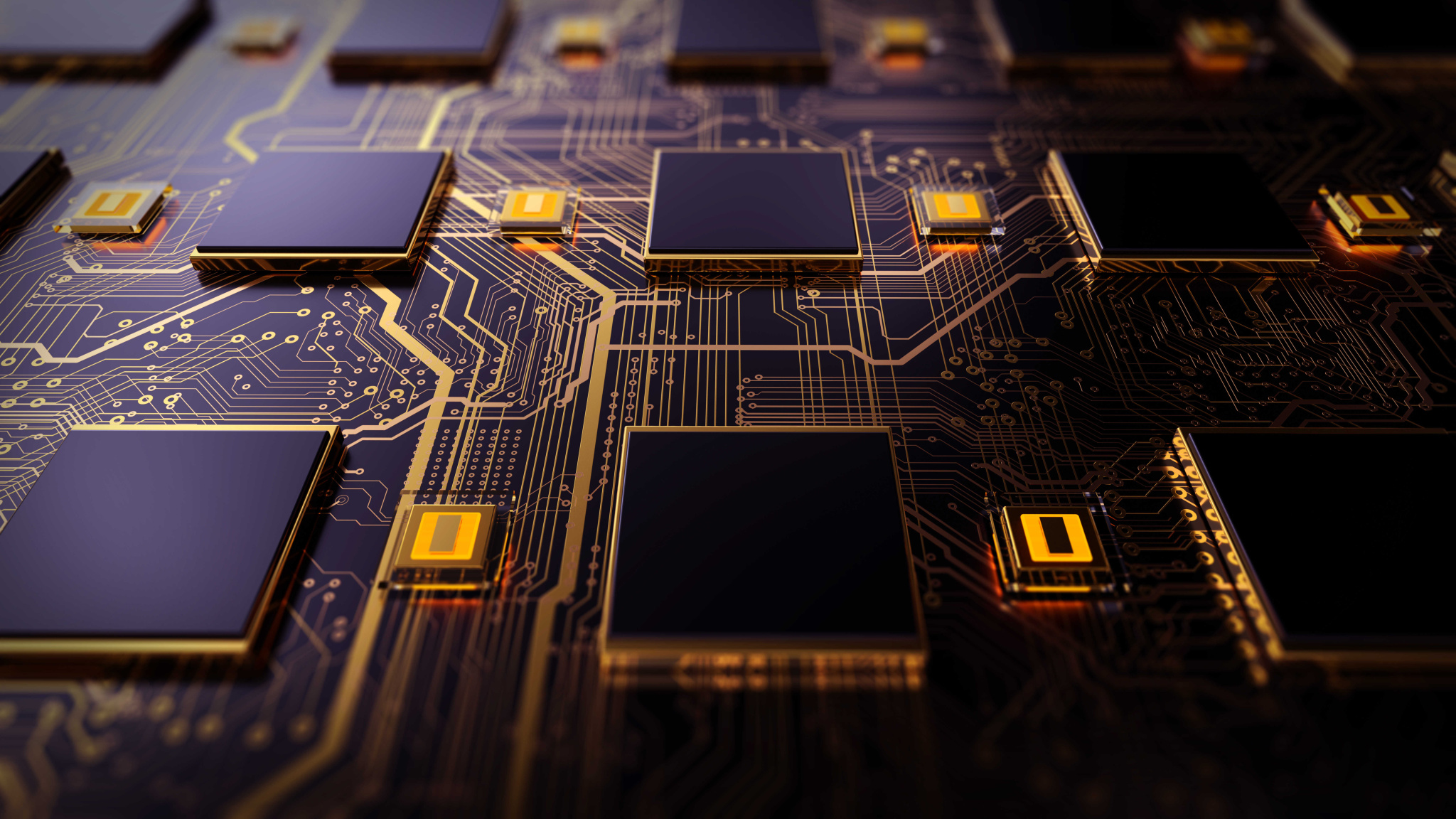

在论坛的开场,方技术长随即开宗明义地指出,随着摩尔定律趋缓,单纯追求晶片制程微缩的道路已日益艰难。传统上,工程师在系统级晶片(SoC)与系统单板(SoB)之间做选择,前者整合度高但开发成本与周期惊人,后者虽灵活却牺牲了体积与功耗。他接着强调,系统级封装(SiP)技术正是在此背景下应运而生的最佳解方,它透过先进的封装技术,将MCU、记忆体、感测器、电源管理晶片,甚至天线等不同制程、不同材质的「小晶片(Chiplet)」与被动元件,整合在一个高度紧凑的封装体内。

图说:USI环鸿科技技术长方永城 (John Fang)应邀成为MCU 论坛演讲嘉宾。

「我们观察到一个很明显的趋势,就是上游的封装测试厂想往下游走,而我们这些比较下游的系统厂则想往上游走,大家最终会碰在一起。」技术长在演讲中生动地描述了产业的动态。他坦言,许多传统OSAT同业也开始投入SiP领域,而环鸿科技最大的差异化优势,则在于其深厚的「系统设计能力」。凭借身为全球顶尖EMS/ODM厂的经验,环鸿科技提供的SiP服务,远不止于后段的封装代工。「在前端的硬体、软体设计,我们也都有能力可以处理」技术长自信地表示。这意味着环鸿科技能从客户的应用场景出发,提供从晶片选用、电路设计、软体驱动、系统验证到最终量产的一站式解决方案,这正是单纯的封装厂难以企及的系统级价值。

「微小化」不只为轻薄,更为高效能与新应用

当谈及SiP的核心效益,技术长首先聚焦于「微小化」。他以环鸿科技操刀的智慧手表为例,透过将MCU、LPDDR2记忆体及76个被动元件整合,成功将功能电路面积从221mm²大幅缩减至81mm²,尺寸锐减63.4%。另一个极端的例子即是胶囊内视镜,SiP技术将其内部复杂的电路极致压缩,使胶囊尺寸得以缩小,直接提升了医疗体验的舒适性。

应用实例列表

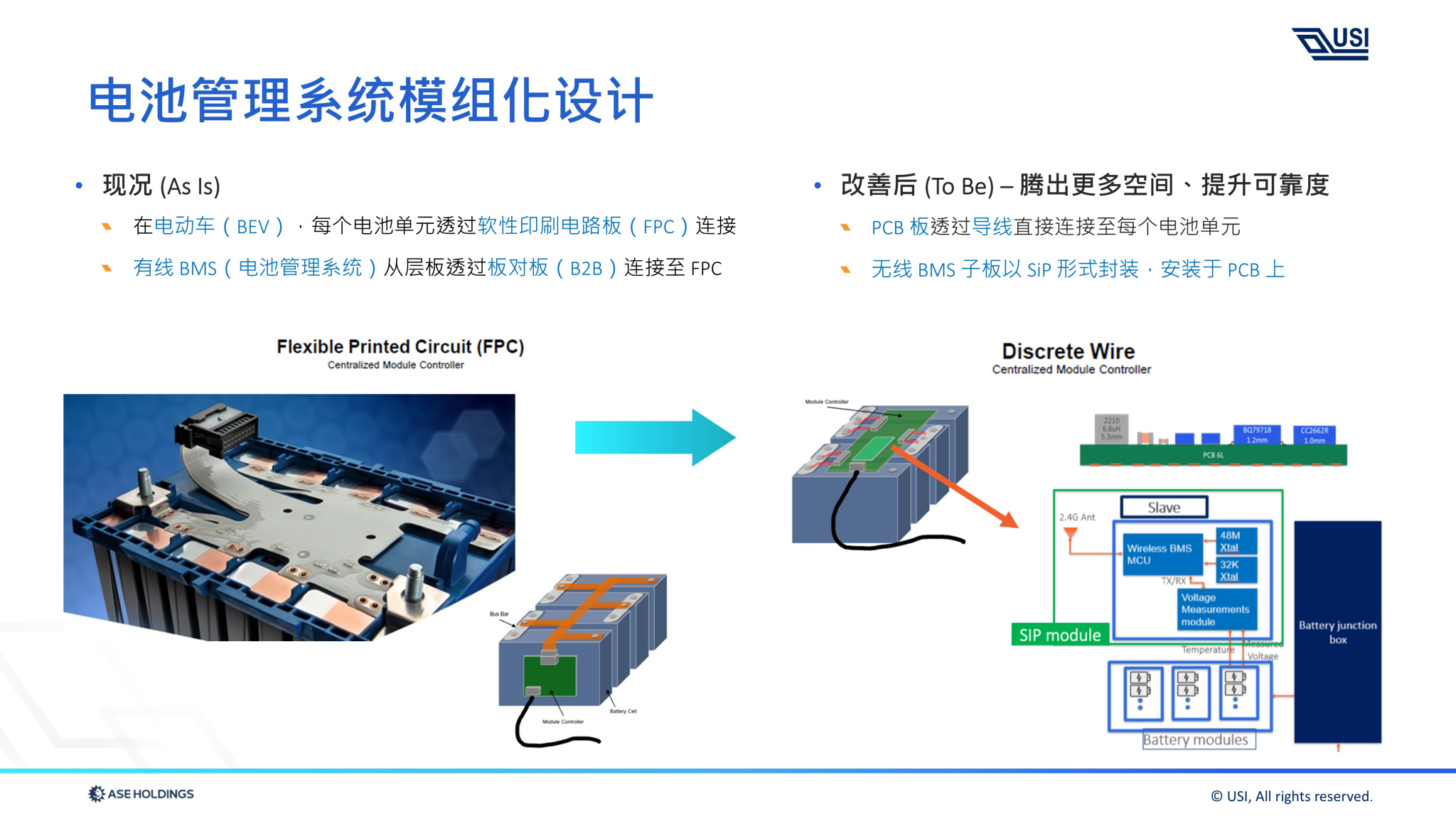

- 电动车电池管理系统(BMS):从传统 FPC 连接架构,进化为无线 SiP 模组,提升可靠性并节省安装空间。

- 医疗胶囊内视镜:以 SiP 技术整合影像处理与无线传输功能,达到极致小型化。

- 混合式智慧手表:尺寸缩小 63.4%,简化主板设计,并保留全功能运作。

图说:SiP技术让胶囊内视镜的微小化成为可能。

然而,微小化的意义远不止于满足消费性电子对「轻薄短小」的追求。方技术长分享了与AI客户的合作经验,揭示了微缩的另一层战略意义。「大家想象一下,以前AI伺服器的板子那么大,我们现在也要想办法把它缩小。为什么?因为要腾出空间来放Power(电源)。」他一语道破关键。

在AI算力需求呈指数级增长的今天,功耗与散热已成为最大瓶颈。透过SiP将元件间的路径缩到最短,不仅提升了讯号传输效能,更直接降低了整体功耗。「一个国家的算力,其实是受到它的电力影响。」方技术长指出,在AR/VR眼镜、智慧手表这类电池容量极其有限的装置上,功耗的降低更是决定产品续航力与使用者体验的生死线。SiP 不仅能透过先进制程减少漏电,还能在 PCB 设计层面缩短连接距离,达成整体性能与能源效率的双重提升。

模组化赋能创新,加速产品上市进程

SiP的第二大支柱是「模组化」。透过将一个预先验证过、功能完整的MCU系统封装成标准化模组,客户在开发新产品时,无需再为复杂的底层电路耗费心神。技术长以电动车的电池管理系统(BMS)为例,传统方案需透过复杂的软排线(FPC)连接,而环鸿科技则开发出无线BMS SiP模组,不仅可靠度更高,更为寸土寸金的电池包释放出宝贵空间。另外,在复合式智慧腕表的案例中,客户的主机板设计被极大简化,只需将SiP模组、机芯与震动马达组装即可,大幅降低了开发门槛与组装难度。

图说:将BMS模组化,不仅提升可靠度,更节省了电动车内部空间。

「Time to Market,这是最大的好处。」技术长总结道。一个预先通过认证的SiP模组,如同一个即插即用的乐高积木,能让客户专注于自身的核心应用与软体开发,省去大量硬体验证时间。这不仅保护了模组内的IP,更让产品的迭代与创新速度呈倍数提升。最终,SiP模组方案能带来约30%的厚度缩减、高达40%至60%的面积缩减,并能根据产品ID需求,客制化成任何「想象得到或想象不到的形状」。简而言之,系统级封装 SiP的优势,可以浓缩成三大面向:

- 模组化 — 简化组装流程,缩短开发时程(Time-to-Market),并强化知识产权保护。

- 微小化 — 提供更大设计自由度,让系统整合更灵活。

- 商品化 — 厚度缩减达 30%,面积缩小 30%,并能因应不同场景需求打造客制形状。

图说:系统整合采用SiP的重点核心价值。

「系统整合能力」决定 MCU 的未来

在演讲的尾声,方技术长重申,环鸿科技提供的SiP模组是软硬整合的完整系统,从底层的RTOS、Android/Linux驱动,到上层的云端服务对接与各国法规认证,皆在环鸿科技的服务范畴。这场演讲为「MCU再进化」的论坛主轴提供了最强而有力的注解,MCU的未来,将由系统整合能力定义。当智慧控制无所不在,环鸿科技正以「封装系统」的独特能力,扮演着那个为万千智慧装置赋能的关键「父亲」角色,着实为产业的下一代发展奠定扎实基础。

跟紧产业脉动

随时掌握第一手产业创新科技、应用与深度新闻

订阅 USI 博客

随时掌握第一手产业创新科技、应用与深度新闻