搜寻

- 06/20/2025

活动|【宽能隙半导体技术论坛】为AI巨兽打造强力心脏:模组化与微小化如何革新伺服器电源效率

主讲者:方永城John Fang, Ph.D., 技术长暨资深副总

在6月12日当天,受到产业媒体伙伴「新电子」的邀请,我们的方技术长有幸前往担任「宽能隙半导体技术趋势暨产业应用高峰论坛」的主讲者之一,向产业界的各位先进分享关于AI领域的技术发展,特别是电源供应的议题。当我们谈论高效能运算(HPC)与AI时,脑中浮现的往往是更快的处理器、更大的高频宽记忆体(HBM),以及如3D IC堆迭、扇出型晶圆级封装(Fan-Out)等先进封装技术 。然而,在这场算力的军备竞赛背后,一个更根本的挑战正日益严峻,那就是「供电」。

AI被形容为「吃电怪兽」绝非夸饰,我们迫切需要更创新的方法来提升能源效率 。 USI环旭电子的电源模组事业占有举足轻重的地位,主要应用于两大高成长领域:电动车(EV)与AI伺服器(AI Server)。今天,我们将深入探讨这个关键议题:供电,聚焦于AI伺服器的电源效率挑战与我们的解决方案。在本次的讲座中,方技术长着重在分享透过模组化(Modulization)与微小化(Miniaturization),环旭电子如何为AI伺服器打造一颗更强效、更节能的动力心脏 。

指数级增长的功耗:AI时代的能源警钟

首先,方技术长特别提出,必须正视问题的严重性。GPU的功耗正在以惊人的速度飙升。以NVIDIA的产品为例,从A100到H100,功耗在短短一个世代内就增加了75% 。而最新的B200功耗已高达1,200W,未来的R200预计将达到1,800W 。AMD与Intel的产品线也呈现出类似的趋势,功耗增幅动辄50% 。

这不仅仅是用在单一晶片的数字。xAI的创办人马斯克(Elon Musk)曾提到,其Grok 2模型需要20,000颗NVIDIA H100 GPU,而Grok 3更需要高达100,000颗 。这意味着仅GPU就需要约100MW的电力,若加上伺服器与冷却系统,其位于曼菲斯的「超级计算丛集」甚至向当地电力公司申请了150MW的电力,足够供应数万户家庭使用 。

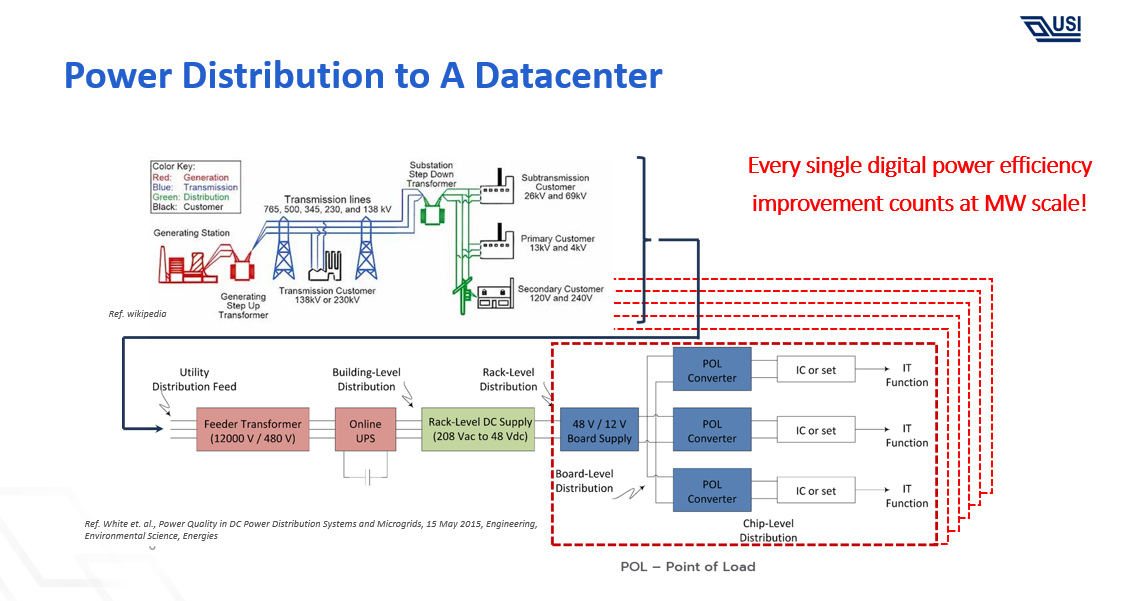

在一个典型的数据中心中,电力转换(Power Conversion)本身就占了总能耗的11% 。当我们面对百万瓦(Megawatt)级别的总功耗时,任何一点效率的提升都至关重要 。

传统方法「水平并排(Side-by-Side)」的极限:为何2%的进步远远不够?

传统上,为了提升电源效率,工程师会在晶片层级进行优化。例如:

- 使用损耗更低的功率级(Power Stage),可提升约1.6%的效率 。

- 采用直流电阻(DCR)更低的电感(Choke),可提升约0.2% 。

- 调整电压调节器(VR)的开关频率,再提升约0.2% 。

综合这些努力,我们可以获得大约2%的效率改善 。然而,这在动辄损耗20%甚至40%的系统中,无疑是杯水车薪 。我们需要的是一场真正的技术突破 。此外,传统设计还面临严峻的空间限制 。目前的CPU设计,例如一个320W的CPU可能需要8相(8-phase)供电 。当下一代CPU升级到400W时,则需要10相供电 。对于业界来说,最巨大的挑战,即是要在同样大小的PCB面积内,塞进更多的供电元件,还要解决散热、电力传输限制与成本上升等问题。

典范转移:从「水平并排」到「垂直整合」的革命

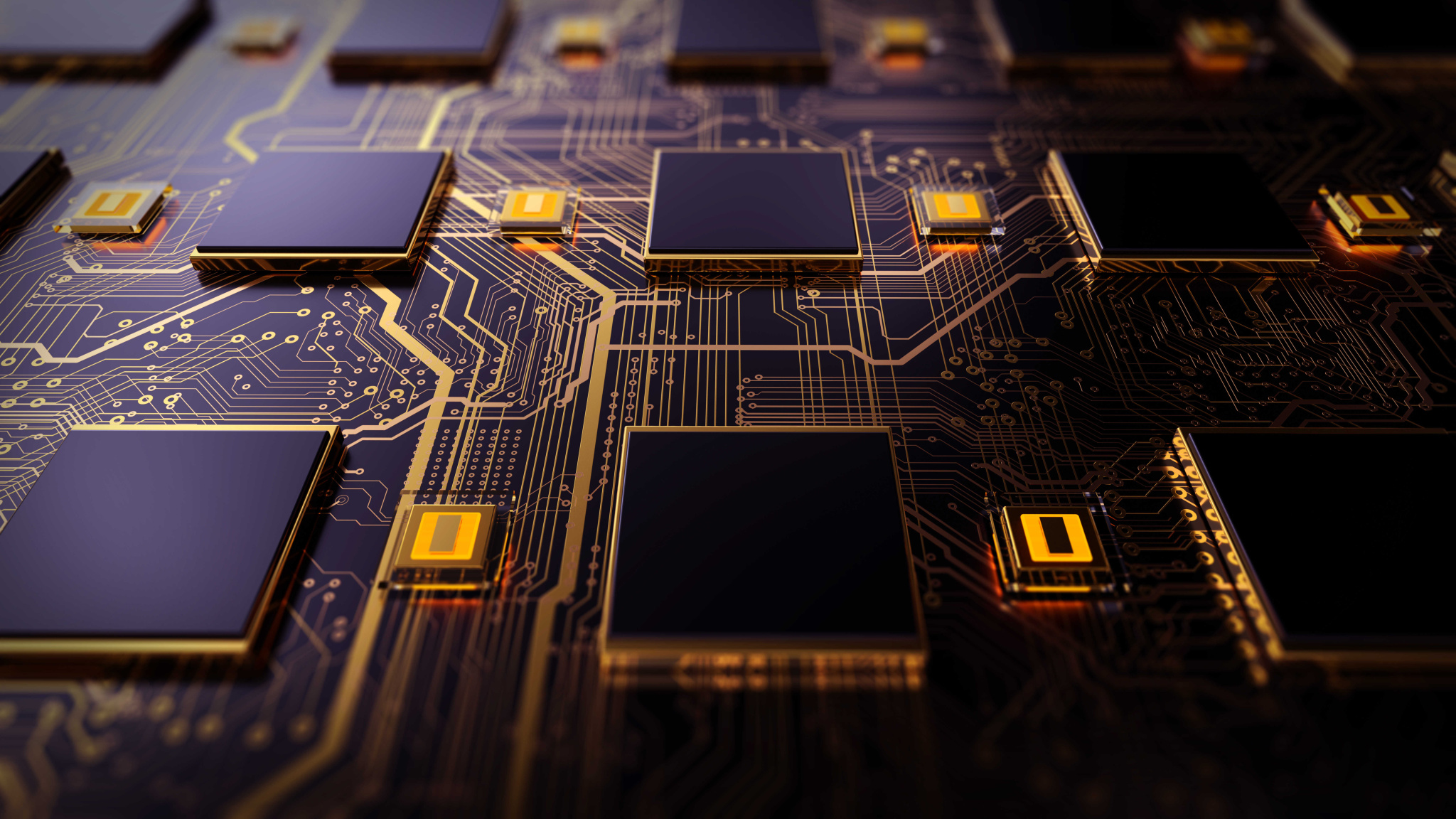

为了解决上述困境,电源解决方案的设计思维正在经历一场典范转移。方技术长进一步提出目前的技术演进路径如下: 离散元件并排 -> 堆迭式电源模组 -> 垂直整合 -> 积体电路级电压调节器(IVR)

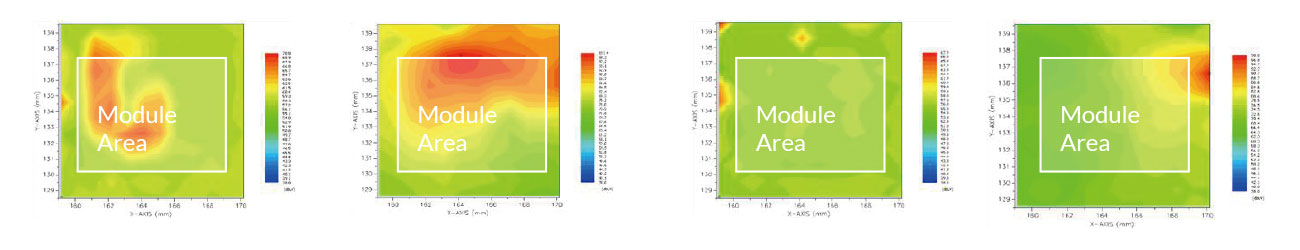

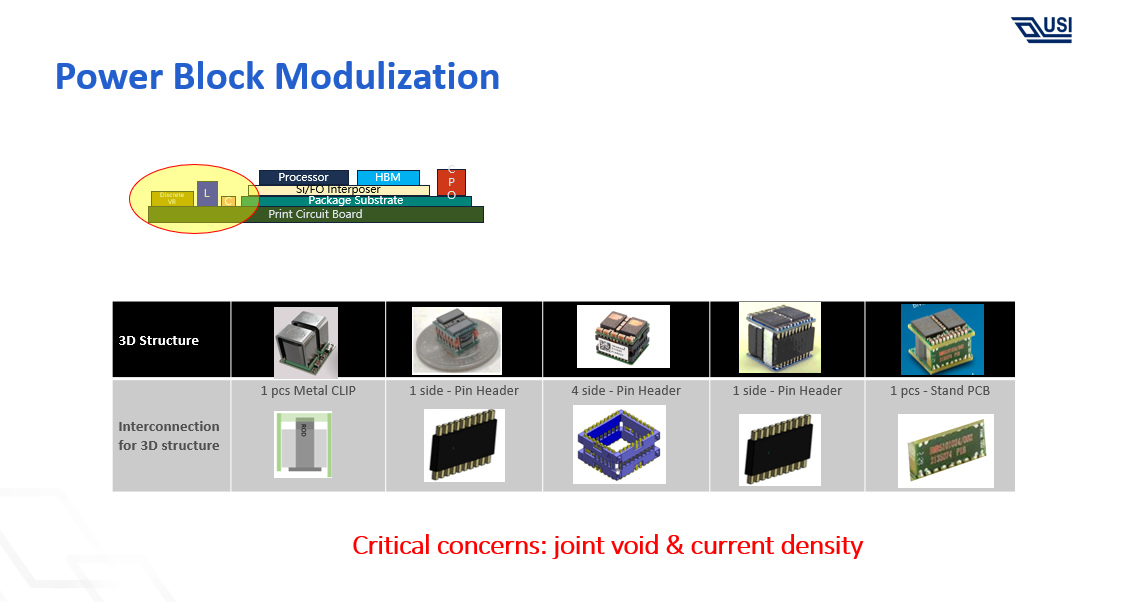

第一步:堆迭式电源模组(模组化) 解决方案是将离散的DrMOS、电感、电容等元件,预先整合成一个3D堆迭的电源模组(Power Block) 。这种模组化设计不仅节省了PCB空间,也为标准化生产铺平了道路 。市场上已有多种此类解决方案,但仍需克服如接合空隙(joint void)与电流密度等制程挑战 。

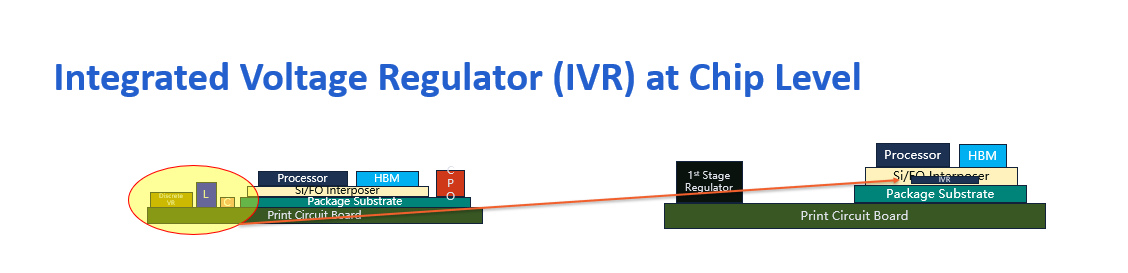

第二步:垂直整合VRM(微小化) 这才是真正的革命。我们不再将电源模组「并排」放置在处理器旁边,而是将其「垂直整合」到处理器封装的下方,让电源无限靠近负载点(Point-of-Load) 。

这种"垂直整合电压调节模组(Vertically Integrated VRM)"带来了惊人的效益:

- 尺寸与路径缩短:VRM直接位于SoC下方,电力传输路径极短,大幅降低了铜损(I2R Loss) 。与传统并排设计相比,占用面积(footprint)缩小了25% 。

- 效率巨幅提升:在一个1080W的TDP测试中,并排设计的路由功率损耗高达12%,而垂直整合的powerSIP方案则骤降至6%,损耗直接减半!

- 电源密度翻倍:电流密度从并排设计的0.4 A/mm²,提升至垂直设计的0.6 A/mm² 。

- 这种设计已经通过了严苛的可靠度测试,包括uHAST-96hr与TCT-1000次循环等,证明了其在商业应用上的可行性 。

终极未来:整合在晶片中的IVR

- 零离散元件:体积极小,可以直接安装在SoC基板内部,甚至在BGA的下方,厚度可薄至100um 。

- 极速响应:拥有比传统设计快1000倍的动态电压调节(DVS)能力,能在奈秒(nanosecond)内响应负载变化,提供最精准的电压,从而消除不必要的功率浪费 。

- 消除损耗与外部元件:由于极度靠近负载,几乎消除了I²R损耗,并且不再需要大量外部的解耦电容,进一步降低了系统成本与复杂度 。

从系统到封装,为未来AI打造高效能绿色引擎

现今的能源供应趋势已经相当明确。特斯拉(Tesla)在其AI硬体中,已将电源元件直接放置在GPU下方。AMD、Microsoft也都在其下一代AI伺服器中导入类似的规格,甚至有厂商正在开发将VRM直接整合进处理器硅晶片(Silicon)中的IVR(Integrated Voltage Regulator)技术。

整个电源转换的路径正在不断演进,从机柜级的 48V 输入,降压至主机板的 12V 或直接 48V 供电,最终降至晶片所需的核心电压。在这条链路的每一个环节,微小化与效率提升都是我们技术研发的主轴。

方技术长最后总结表示,为了应对AI时代的算力与功耗挑战,电源设计正从传统的水平并排(Side-by-Side),走向革命性的垂直整合(Vertical)。这不仅仅是元件的重新排列,更是透过结构创新实现的空间、路径与效率的全面最佳化。这条路径的核心精神,就是透过模组化简化设计复杂度,并透过微小化缩短物理距离、降低能量损耗。唯有如此,我们才能为这个算力驱动的未来,打造一颗兼具强大性能与绿色节能的终极心脏。

跟紧产业脉动

随时掌握第一手产业创新科技、应用与深度新闻

订阅 USI 博客

随时掌握第一手产业创新科技、应用与深度新闻