搜尋

- 02/11/2025

突破性能瓶頸:高效能運算系統的雙重挑戰

在當今科技飛速發展的時代,高效能運算(High-Performance Computing, HPC)正以其強大的計算能力,不斷突破各個領域的界限。HPC通過使用由成千上萬個處理器核心組成的超級計算機或計算機集群,執行複雜的計算任務,這些任務通常涉及大量的數據輸入,必須具備大量算力和高速數據處理能力。USI環旭電子在這一波市場角逐中,瞄準AI領域的高度運用,以我們自身的強項「3D封裝技術」切入市場,應用在多項HPC模組中。接下來,本文將從HPC的簡介、挑戰與創新等方面,從正反兩面探討開發HPC最被重視的議題。

Fig.1 USI 環旭電子 3D 封裝技術

高效能運算 (HPC) 簡介

HPC是利用超級計算機實現並行計算的理論、方法、技術以及應用的一門技術科學。處理器、內存和存儲技術的不斷創新,為HPC系統提供了強大的計算資源。現代處理器採用多核設計,具備更高的並行處理能力。內存和存儲技術也在不斷進步,如DDR5內存、PCIe 4.0存儲等,提供了更高的數據傳輸速度和更大的容量,滿足HPC系統對高帶寬和低延遲的需求。

HPC的應用領域廣泛,涵蓋科學研究、天氣預報、模擬等多個方面。它的多樣化應用,使得各個領域都能夠受益於其強大的計算能力。然而,儘管取得了顯著的進步,但在設計和部署HPC系統時仍面臨諸多挑戰。

高效能運算 (HPC) 的供電挑戰

高效能運算系統正面臨著功耗和散熱兩大嚴峻挑戰。這些系統通常由數量龐大的處理器組成,每個處理器都消耗大量電力,這使得降低能量耗損成為首要任務。傳統上,為了降低能量耗損,系統會採用高電壓供電,然後在微處理器前進行多階段轉換為較低的電壓。這個過程中,從DC-DC轉換器到微處理器的路徑佈線耗損扮演著關鍵角色。這些轉換器負責將12V或48V的直流總線電壓降低到處理器核心所需的特定電壓,同時將電流提升到所需的水平。

多階供電網路 (PDN) 的損耗與影響

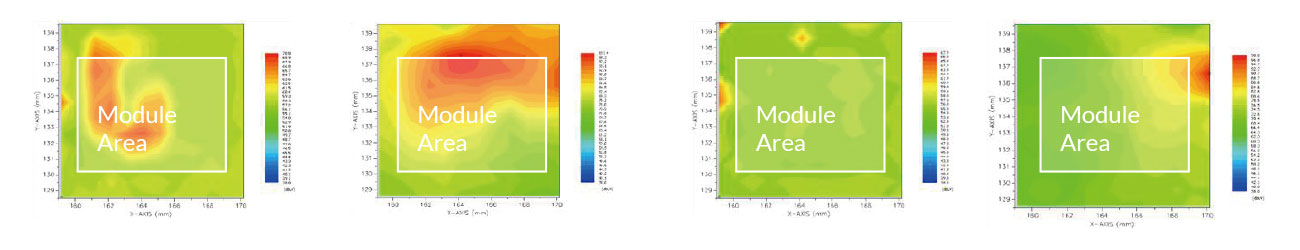

即使穩壓器只需向晶片短距離供電,多階供電網路(PDN)仍然會因為電源軌上的電阻而產生損耗(I²R),進而導致散熱問題。這些損耗也包括電感和電容造成的影響。因此,供電設計中最重要的因素之一是穩壓器在PCB上的位置,這直接影響到饋入處理器引腳的電源軌上的電阻大小。

為了盡可能靠近負載點(POL)來減少電阻,垂直整合的電壓調節模組(VRM)成為了當前熱門的解決方案。這種模組將負責電壓轉換的功率級、管理模組中電流和熱量的磁性元件,以及在電源進入處理器前調節電源的電容器整合在同一個模組中。這意味著VRM可以放置在物理上更靠近POL的位置,從而有效地減少電流損失和功率損耗。

Fig.2 HPC 高效能運算系統的供電損耗及散熱是重要因素

電壓調節模組 (VRM) & 垂直電源傳輸 (VPD)

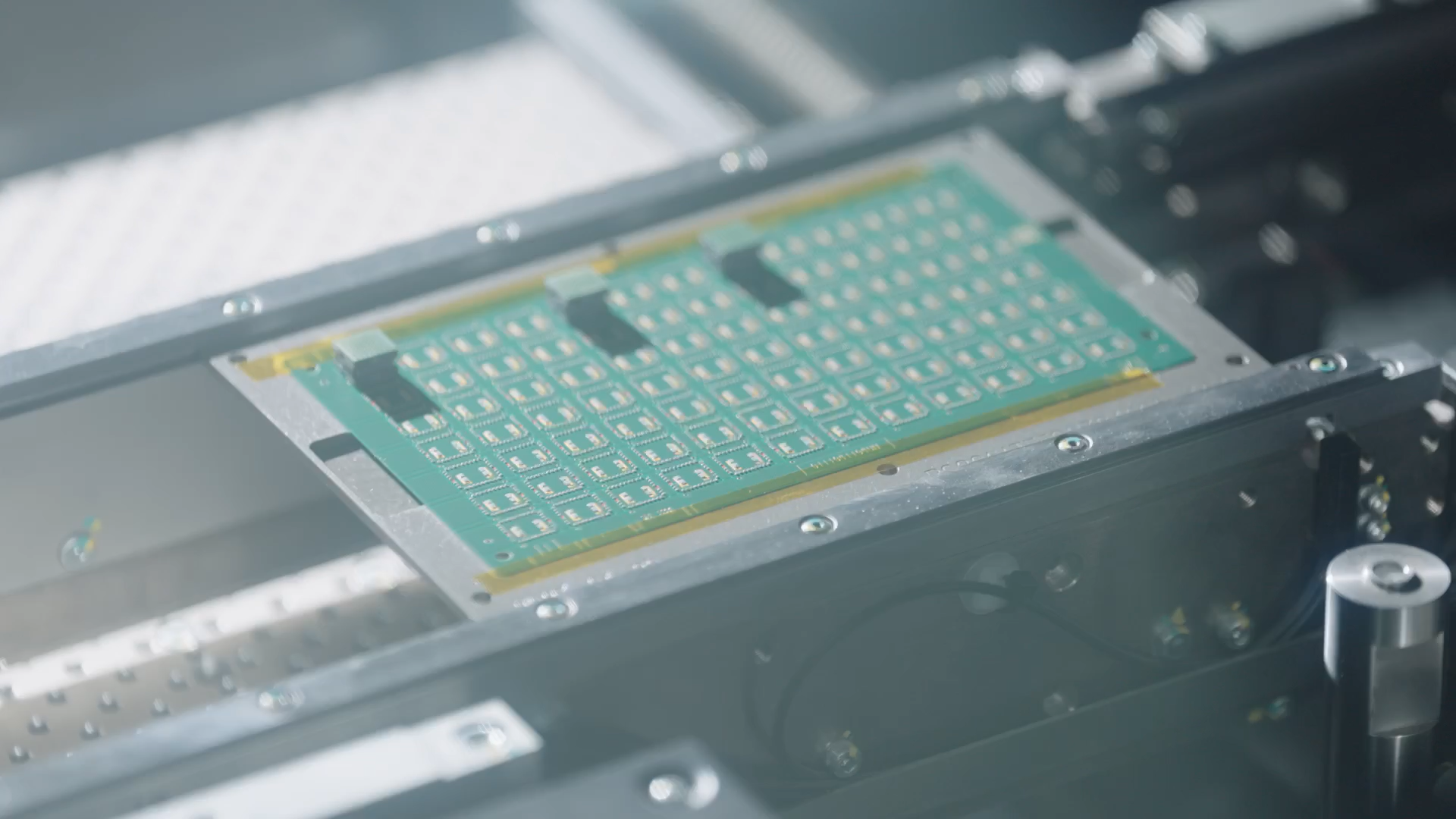

穩壓器模組(VRM)主要由三個部分組成:電容器、電感器和功率級。例如,雙相功率模組,則是將多相降壓穩壓器的兩個相位的元件整合到一個基板上,形成一個單一裝置,並以陣列方式部署,構成一個多相系統。隨著AI加速器在效能和功率需求上不斷提升,功率級的數量可能會進一步增加。

除了元件整合和效能提升,為AI加速器供電的新趨勢是垂直供電,也稱為背面供電。垂直電源傳輸(VPD)技術將電源穩壓器直接移到PCB背面處理器的下方。透過較短的垂直路徑傳輸電源,VPD可以大幅降低PDN(電源傳輸網路)的電阻並減少損耗,從而在較高電流和較低處理器核心電壓下達到更高的電源效率。此外,由於VPD消除了PCB上的空間佔用,AI處理器設計人員可以增加記憶體和I/O線路,從而進一步提升處理效能。

承上兩大解決方案,各有優劣之處,因此,運用最適合客戶需求的解決方案才是優先考量。如何設計和部署高效能運算系統,以及如何有效地管理和優化功耗、散熱和資源,是成就高效算力系統的必經之路。

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞