搜寻

- 02/11/2025

突破性能瓶颈:高效能运算系统的双重挑战

在当今科技飞速发展的时代,高效能运算(High-Performance Computing, HPC)正以其强大的计算能力,不断突破各个领域的界限。HPC通过使用由成千上万个处理器核心组成的超级计算机或计算机集群,执行复杂的计算任务,这些任务通常涉及大量的数据输入,必须具备大量算力和高速数据处理能力。USI环旭电子在这一波市场角逐中,瞄准AI领域的高度运用,以我们自身的强项「3D封装技术」切入市场,应用在多项HPC模组中。接下来,本文将从HPC的简介、挑战与创新等方面,从正反两面探讨开发HPC最被重视的议题。

Fig.1 USI 环旭电子 3D 封装技术

高效能运算 (HPC) 简介

HPC是利用超级计算机实现并行计算的理论、方法、技术以及应用的一门技术科学。处理器、内存和存储技术的不断创新,为HPC系统提供了强大的计算资源。现代处理器采用多核设计,具备更高的并行处理能力。内存和存储技术也在不断进步,如DDR5内存、PCIe 4.0存储等,提供了更高的数据传输速度和更大的容量,满足HPC系统对高带宽和低延迟的需求。

HPC的应用领域广泛,涵盖科学研究、天气预报、模拟等多个方面。它的多样化应用,使得各个领域都能够受益于其强大的计算能力。然而,尽管取得了显著的进步,但在设计和部署HPC系统时仍面临诸多挑战。

高效能运算 (HPC) 的供电挑战

高效能运算系统正面临着功耗和散热两大严峻挑战。这些系统通常由数量庞大的处理器组成,每个处理器都消耗大量电力,这使得降低能量耗损成为首要任务。传统上,为了降低能量耗损,系统会采用高电压供电,然后在微处理器前进行多阶段转换为较低的电压。这个过程中,从DC-DC转换器到微处理器的路径布线耗损扮演着关键角色。这些转换器负责将12V或48V的直流总线电压降低到处理器核心所需的特定电压,同时将电流提升到所需的水平。

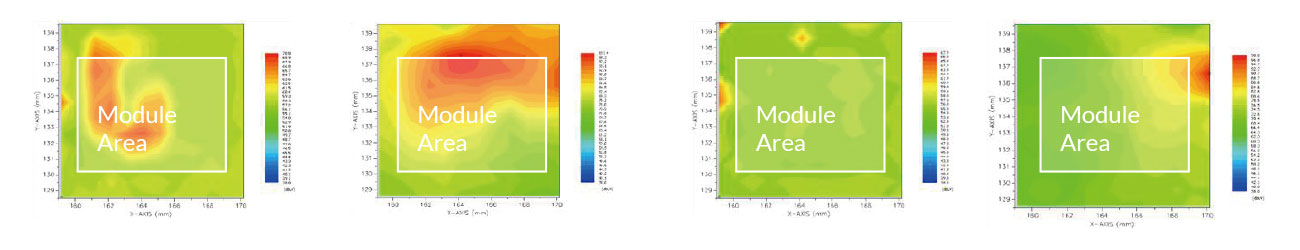

多阶供电网路 (PDN) 的损耗与影响

即使稳压器只需向晶片短距离供电,多阶供电网路(PDN)仍然会因为电源轨上的电阻而产生损耗(I²R),进而导致散热问题。这些损耗也包括电感和电容造成的影响。因此,供电设计中最重要的因素之一是稳压器在PCB上的位置,这直接影响到馈入处理器引脚的电源轨上的电阻大小。

为了尽可能靠近负载点(POL)来减少电阻,垂直整合的电压调节模组(VRM)成为了当前热门的解决方案。这种模组将负责电压转换的功率级、管理模组中电流和热量的磁性元件,以及在电源进入处理器前调节电源的电容器整合在同一个模组中。这意味着VRM可以放置在物理上更靠近POL的位置,从而有效地减少电流损失和功率损耗。

Fig.2 HPC 高效能运算系统的供电损耗及散热是重要因素

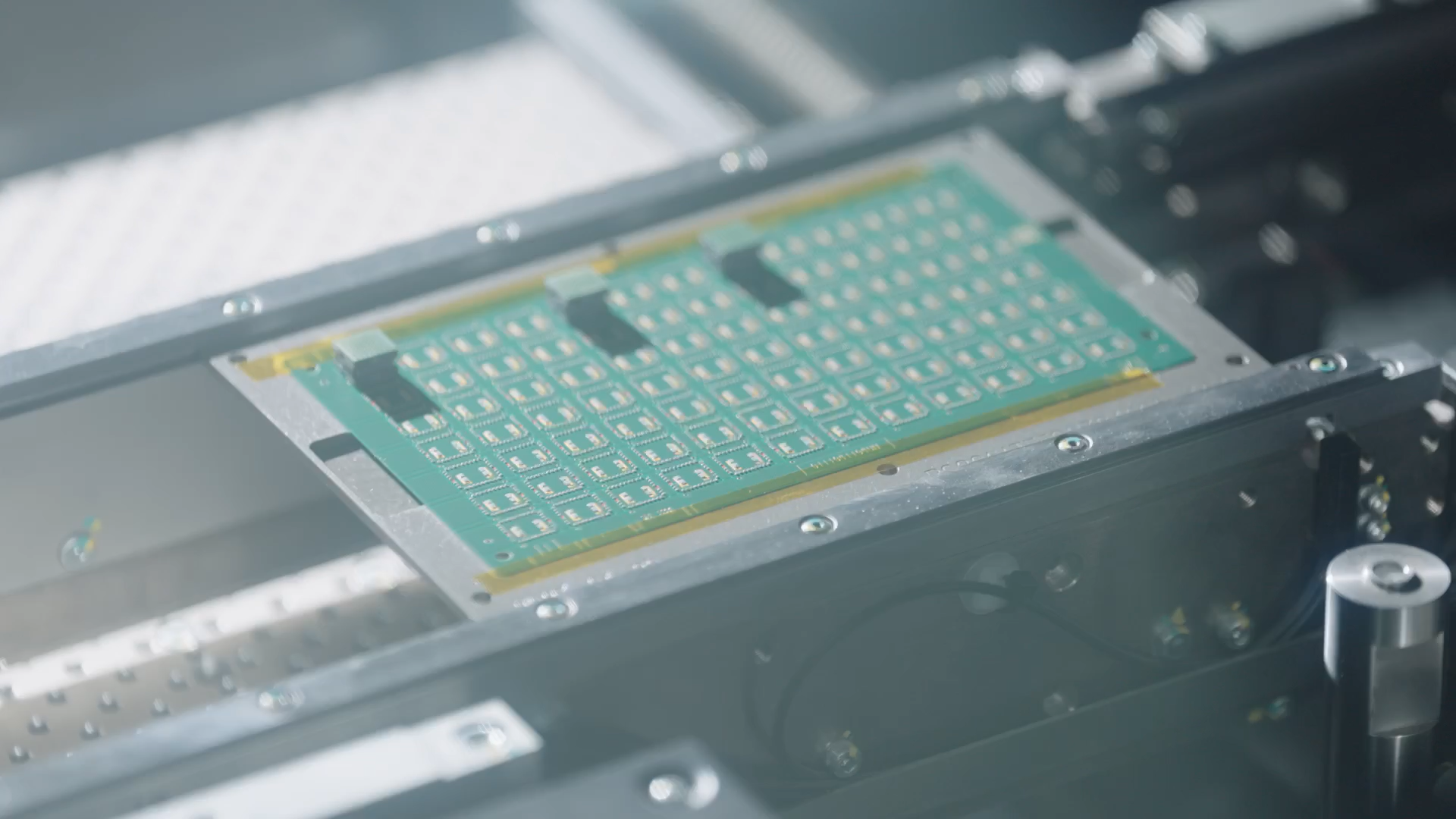

电压调节模组 (VRM) & 垂直电源传输 (VPD)

稳压器模组(VRM)主要由三个部分组成:电容器、电感器和功率级。例如,双相功率模组,则是将多相降压稳压器的两个相位的元件整合到一个基板上,形成一个单一装置,并以阵列方式部署,构成一个多相系统。随着AI加速器在效能和功率需求上不断提升,功率级的数量可能会进一步增加。

除了元件整合和效能提升,为AI加速器供电的新趋势是垂直供电,也称为背面供电。垂直电源传输(VPD)技术将电源稳压器直接移到PCB背面处理器的下方。透过较短的垂直路径传输电源,VPD可以大幅降低PDN(电源传输网路)的电阻并减少损耗,从而在较高电流和较低处理器核心电压下达到更高的电源效率。此外,由于VPD消除了PCB上的空间占用,AI处理器设计人员可以增加记忆体和I/O线路,从而进一步提升处理效能。

承上两大解决方案,各有优劣之处,因此,运用最适合客户需求的解决方案才是优先考量。如何设计和部署高效能运算系统,以及如何有效地管理和优化功耗、散热和资源,是成就高效算力系统的必经之路。

跟紧产业脉动

随时掌握第一手产业创新科技、应用与深度新闻

订阅 USI 博客

随时掌握第一手产业创新科技、应用与深度新闻