搜尋

- 04/02/2024

超越毫釐之爭,掌握微小化的藝術

隨著電子產品微小化的需求不斷提升,封裝技術也必須朝向更小、更高效的方向發展。先進封裝技術能夠將多顆裸晶、主動元件、被動元件甚至機電元件整合到單一微型封裝體中,在縮小尺寸的同時,也能提升效能和整體系統功能。在開始探討先進封裝技術之前,您可以先閱讀另一篇文章:系統級封裝(SiP) : 一站式微小化解決方案。本文將接著深入探討系統級封裝 (SiP) 技術,並介紹其複雜的組裝流程,以及其他先進封裝技術,例如系統單晶片 (SoC) 和小晶片模組技術。

系統級封裝SiP製程步驟拆解

SiP系統級封裝製造過程涉及幾個關鍵步驟,通過遵循這些細緻的步驟,製造商可以確保各種電子設備中使用的 SiP 模組的品質、可靠性和長期功能性:

- 主板基材處理

- 首先要讓零件可以牢牢地焊在電路板上,就得先處理基材的表面。這道工序往往由PCB廠先進行處理,接著才交給封裝製造商。通常會包含清潔、粗化表面,以及塗上薄薄的一層金屬 (通常是銅) 來增加導電性。

- 接著,會在處理好的基材上放上「鋼網」。鋼網是一種金屬薄片,上面用雷射切割出跟電子零件大小位置相符的孔洞。

- 最後的印刷,會使用一種黏稠狀的「錫膏」,裡面含有細小的焊錫粉末。透過鋼網的孔洞,錫膏會被擠壓在電路板指定的位置,形成用來焊接零件的焊盤。

- 高密度表面黏著技術 (HD-SMT)

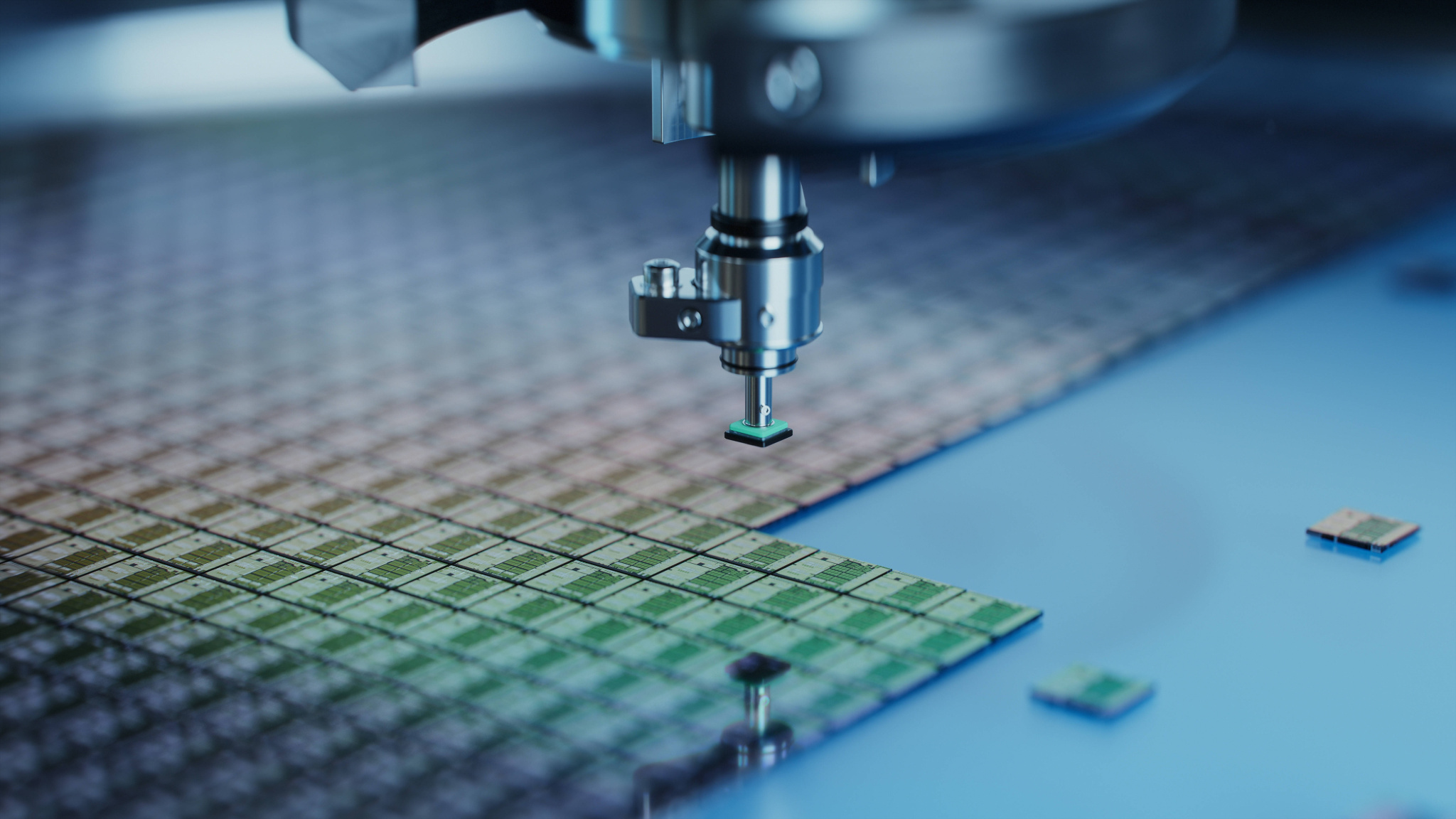

將錫膏印刷在電路基板的表面之後,接著就是將電子元件的焊腳置放在有錫膏的位置,於此階段就會使用到有裝載吸附噴嘴和視覺系統的「高速貼片機」。高速貼片機可以從供料盤或捲軸中個別抓取電子零件,然後非常精準地放在基板上。這個步驟的精準度非常重要,因為任何一點點的偏移都可能造成電路連接不良。之後,運用高溫讓錫膏融化,將電子元件焊接在電路基板上。

深入了解更多:系統級封裝 - 高密度貼裝能力

深入了解更多:系統級封裝 - 高密度貼裝能力

- 元件連結:固晶與打線接合

若要運用在更高階的微小化產品,讓這些電路板上的零件彼此「溝通」,就得靠另外兩種技術:固晶技術 (Die Bonding) 和打線接合 (Wire Bonding)。首先是固晶技術,這個步驟就像蓋房子打地基一樣重要,這時會在基材上塗上極少量的導電膠,就像水泥一樣把地基固定住。然後,再用非常精密的技術把沒有外殼的整合電路 (IC),也就是「裸晶 (die)」放到定位好的基材上,接著施加高溫高壓,讓晶片牢牢地黏在基板上,形成穩固可靠的連接。

另外一種打線接合,則是採用微米等級的金屬線 (通常是銅線、金線或鋁線),並透過焊針或球形接合技術,小心翼翼地將這些金屬線焊接到事先規劃好的焊盤上,達成電路互通。打線接合的優點是靈活度高,可以應付不同高度的零件,在電路板設計上更有彈性。

另外一種打線接合,則是採用微米等級的金屬線 (通常是銅線、金線或鋁線),並透過焊針或球形接合技術,小心翼翼地將這些金屬線焊接到事先規劃好的焊盤上,達成電路互通。打線接合的優點是靈活度高,可以應付不同高度的零件,在電路板設計上更有彈性。

- 封裝階段

在電氣連接形成後,整顆 SiP 模組將用保護材料(通常是環氧樹脂)封裝。這一作法可以保護精密元件免受環境因素(如濕氣、灰塵和物理衝擊)的影響。針對不同需求取向可以採用不同的封裝技術,除了全體封裝(覆蓋整個 SiP模組)外,還可以進行選擇性和階梯式封裝。

深入了解更多:系統級封裝 - 塑封能力、系統級封裝 - 遮罩能力

深入了解更多:系統級封裝 - 塑封能力、系統級封裝 - 遮罩能力

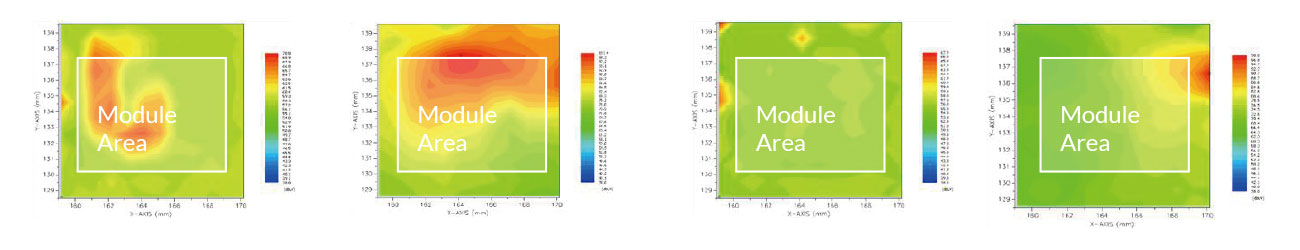

- 測試與檢驗

封裝完成後,SiP模組會進行嚴格的測試,確保功能和效能的正常運作。一般會包含電氣測試,檢查連線和零件有沒有問題,也會用光學檢測和 X光檢測來看封裝材料裡面有沒有瑕疵或空洞。功能測試的部分會模擬實際使用環境,來評估 SiP 模組整體的性能表現。

系統級封裝SiP的優勢

SiP 技術有許多可取之處:

- 尺寸輕薄:可以把很多零件整合在一起,讓電子設備整個變得非常小巧。這對於消費性產品來說非常棒,例如穿戴式裝置和智慧型手機。

- 效能提升:它能夠縮短零件之間的電氣路徑,讓訊號傳輸更快、訊號完整性更好,整台設備的效能也就跟著提升。

- 更可靠耐用:系統級封裝技術可以保護零件免受外力、潮濕、灰塵等外来物影響,讓電子設備更加穩定可靠。

- 快速上市:透過模組化設計,可以同時開發多種產品,並且縮短產品上市的時間。使得品牌客戶,也就是客戶們可以更快搶攻市場商機。

除了SiP,還有哪些微小化解決方案?

系統級封裝(SiP)技術是改變電子行業實現複雜功能的微小化和系統整合的解決方案之一。但是對於客戶、產品甚至預算而言,要選擇哪個解決方案可能存在多樣性。因此,讓我們來看看其他兩種目前市場上討論度極高的封裝解決方案:

環旭電子技術探索篇|微小化技術本質:SoC、Chiplet、SiP

SoC (System on Chip) 系統單晶片

SoC 指的是將各種功能整合到單一晶片上,包含像是處理器、記憶體單元和輸入/輸出介面等重要元件。這種把功能集中在統一平台的做法簡化了整體系統的架構,提升效率並縮小體積。儘管 SoC 技術仍被主流市場採用,但面對不斷變化的功能需求勢必要整合更多新的功能,面對這個問題,SoC技術已經開始出現製程上的瓶頸。

系統單晶片SoC 會面臨什麼挑戰嗎?

現今SoC所面臨最主要的困難是它僵化的製造特性,限制了晶片因應動態需求的靈活性。雖然 SoC 技術能夠整合不同功能,但卻僅限於相同製程技術下的元件。這種缺乏彈性往往需要在進行修改或升級時,投入大量重新設計的功夫,進而導致開發時間延長和成本增加。這些挑戰凸顯了其他微小化技術的特性,例如小晶片模組(Chiplet)和系統級封裝 (SiP)。

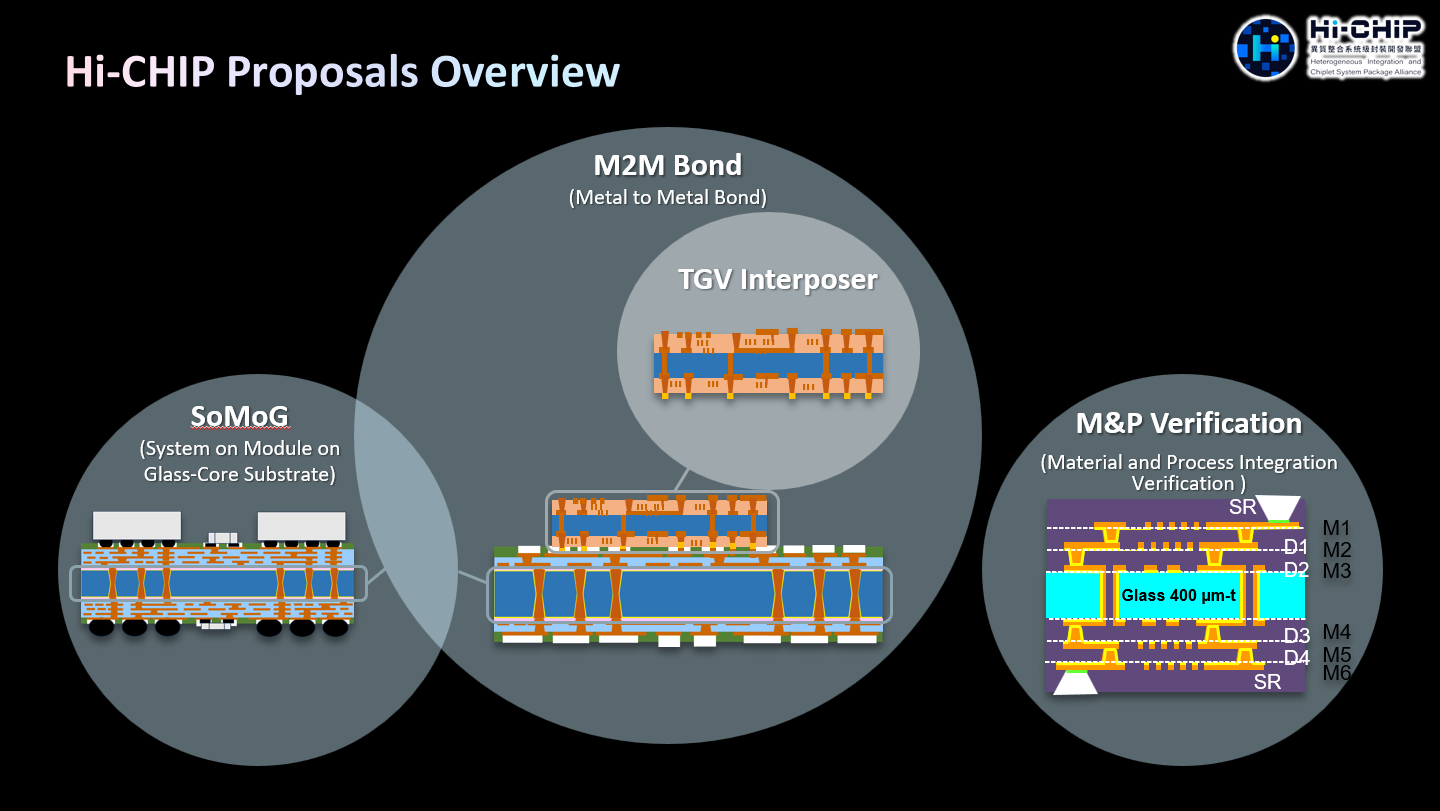

Chiplet 小晶片模組

近年來全球人工智慧 (AI) 應用蓬勃發展,對於高運算力及影像處理模組的需求也急遽增加,而Chiplet技術儼然成為 AI 晶片的首選方案。相較於SoC的封裝方式,它的特色在於能夠提供更大的彈性,因為SoC所有元件都必須採用相同的製程,但Chiplet技術可將採用不同製程的元件整合於一個基板上。這種彈性不僅能提升客製化能力,使得Chiplet技術成為高效運算、AI領域的絕佳選項。

小晶片模組Chiplet會面臨什麼挑戰嗎?

該種製程最主要問題會是在於生產良率與成本,因為要能夠多顆IC組裝於基板上的複雜製程需要極度精密的技術,這相對會提高缺陷率,進而促使成本飆升。此外,如何在緊湊的封裝空間內管理多顆IC的散熱與電力分配也是另一道難題,因為功率密度的提升可能會加劇散熱問題,進而影響整體系統的穩定性。儘管面臨各種挑戰,但是封裝技術正持續研發解決方案,為Chiplet技術在 AI、高效運算等更多領域打造更加堅實的基礎。

產業中有各種先進的封裝解決方案可供選擇,如何選擇皆取決於產品的性能要求。雖然每個解決方案都有其獨特的優勢,但 SiP 在許多應用中脫穎而出。它在微小化、功能性和成本之間取得了卓越的平衡。當進行綜合評量時,SiP其成熟、靈活極具成本效益的解決方案,著實適用於各種應用領域。

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞