Search

- 09/13/2021

System-in-Package (SiP): The most awaited next wave of technology

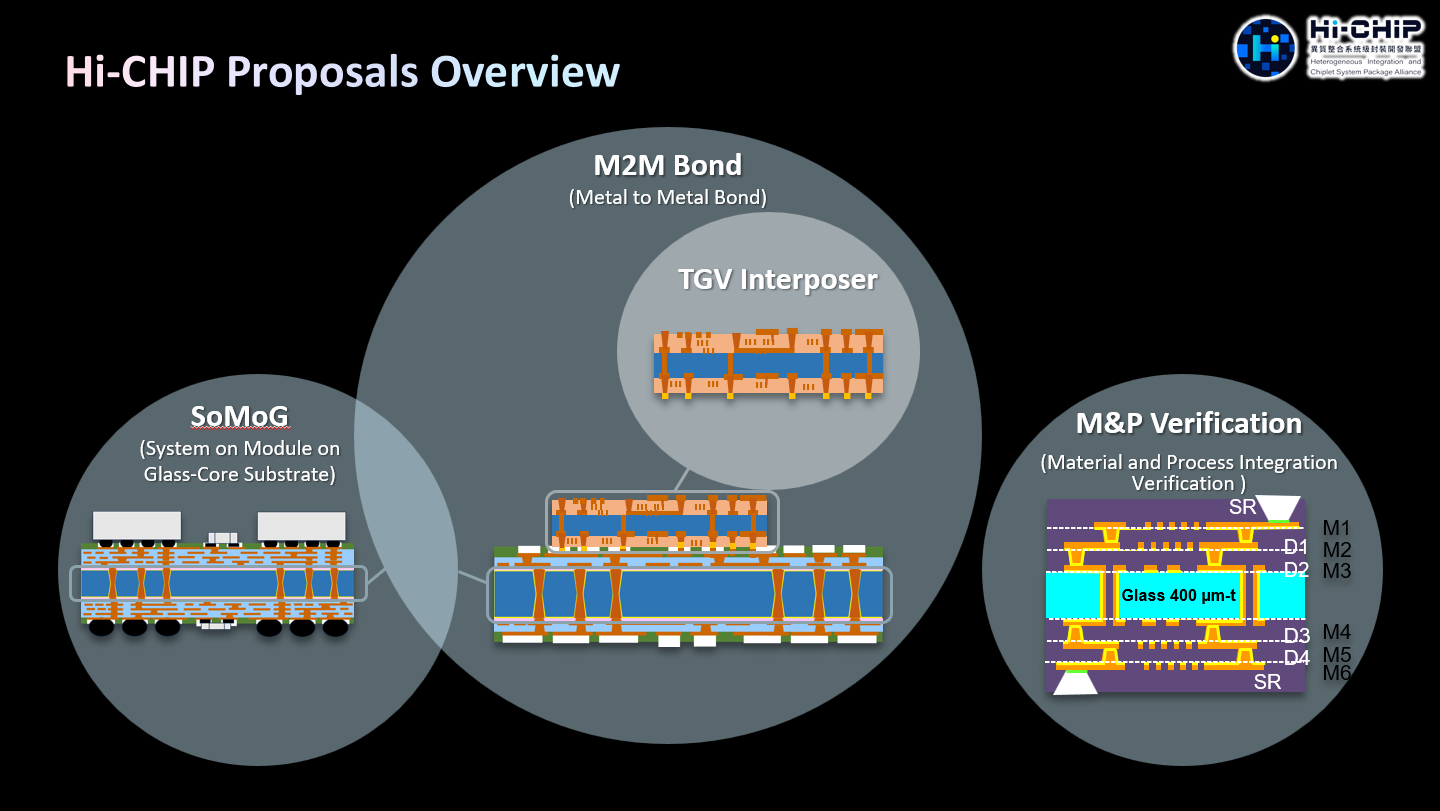

Advanced packaging, which enables a new set of system-level chip designs for a group of applications, is preparing every packaging house. These packages are inclusive of technologies such as System-in-Package (SiP), 3D/2.5D chiplets, and fan-out. In an advanced package, everyone offers multiple options for integrating and assembling complex parts or dies, thus providing ample opportunity to chip customers to differentiate between the design and development of their new IC. IC Vendors are on the lookout for IC packages with better electrical performance and smaller in size.

SiP compared to 3D/2.5D and fan-out is cheaper and has more R&D done on it. SiP is also a lot less challenging as compared to chiplets. A system-in-package brings several elements into one package, enabling the package to function as an electronic subsystem or system. A customer can customize their SiP by incorporating passives, dies, MEMS and antennas as per their requirement. SiPs are used in various products such as smartwatches, smartphones, automotive systems, etc. These SiPs are used widely in WiFi modules, RF Front end, and to provide power management ICs.

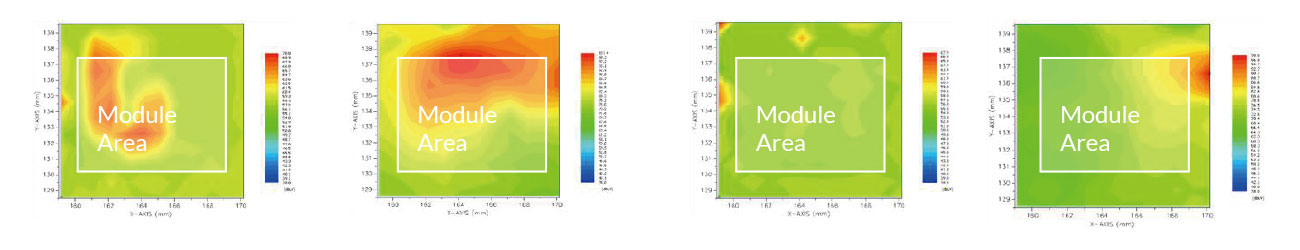

The most popular smartwatch on the market that has integrated a SiP. By taking SiP technology, the company can develop more functions into its smartwatch product generation by generation. A few other forms are of SiPs are being developed, such as Heterogeneous System-in-Package (HSiP). The SiPs developed by USI are a lot different from those produced by OSAT manufacturers. At USI, our strength in SiP lies in the field of product development for system applications. Whereas our OSAT partner, ASE, focuses on innovative waferchip level technologies, USI offers customers a total SiP solution for miniaturized system modules from efficient designs to module manufacturing.

The reason for employing SiP on your product

- Size (XY) Reduction to have more Space for Battery and new functions

- Reduce Thickness (Z) and Weight for Stylish ID Design

- Reduce FATP Difficulty

- Improve Signal Integrity

- EMI Shielding Interference

- Speed up Development

- Better Reliability - Humidity and Mechanical

- Better Logistics and Inventory Management

The present SiP has a long "lead time". Now, USI’s ASSSiP attempts to shorten or decrease the lead time by developing standard SiP products for specific functions or applications. For example, product efficacy can be demonstrated when certain functional blocks can be integrated by SiP/SiM, which can effectively and efficiently reduce the size of the motherboard to make more room for the battery, thus extending battery life.

Keep up with top trending topic

For the latest innovation technology, application

and industry insight.

Subscribe Our Blog

For the latest innovation technology, application

and industry insight.