Search

- 01/13/2025

Front-End Design System (FEDS): From manual to automated, cracking the power integrity simulation puzzle!

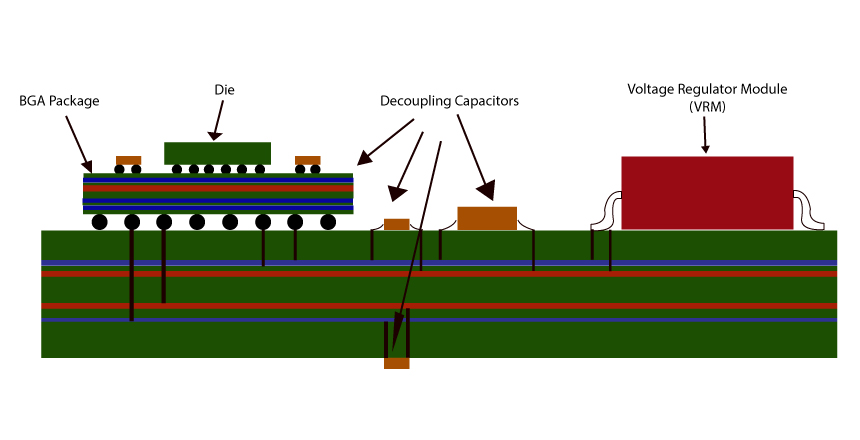

In today's high-speed electronic systems, power integrity ensures that all components receive a stable and accurate power supply, safeguarding system stability and preventing noise or fluctuations. As a critical factor in system performance and reliability, power integrity mandates early-stage system impedance characteristic simulations. However, limited project timelines often pose a challenge in fulfilling the extensive simulation requirements for power design.

Figure 1. The Power Integrity and Distribution Network

(Source from SIERRA CIRCUITS Proto Express)

(Source from SIERRA CIRCUITS Proto Express)

Major IC design houses such as Qualcomm, Intel, and MediaTek have established numerous power integrity simulation items and design objectives to guarantee system stability. The escalating number of simulation items underscores the necessity of power integrity design and verification for hardware and simulation engineers.

Challenges in Power Integrity Simulation

The surge in power integrity demands has presented hardware and simulation engineers with several challenges:

- Time and resource constraints: Traditional manual simulations are time-consuming and require professional engineers. The increasing number of simulation items prolongs design cycles and impacts time-to-market.

- Error rates and inconsistent quality: Manual setup is prone to errors, leading to inconsistent results and redundant simulations, thus wasting resources.

- Managing large-scale simulation requirements: Each chip has distinct power design needs, necessitating customized settings for each simulation item.

- Increasing design complexity: Enhanced processor performance demands more stringent power requirements. Engineers must consider additional factors such as decoupling capacitors and power and ground plane integrity.

Power Integrity Simulation System (FEDS-PI)

Our Power Integrity Simulation System (FEDS-PI) is built upon an automated workflow, significantly reducing manual setup time and human errors. With a user-friendly interface, hardware engineers can effortlessly complete numerous simulation tasks. We've established an optimized power integrity design strategy and conducted internal LMS training to promote the adoption of this automated system, streamlining cross-departmental operations and enhancing simulation efficiency and output. Consequently, power integrity designs can be completed within tighter timelines.

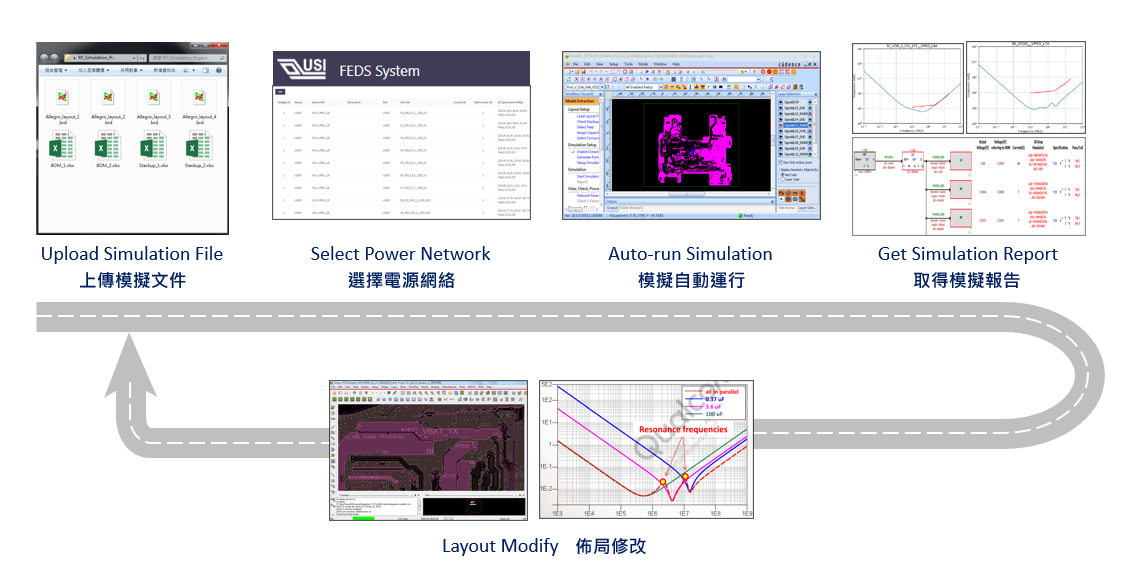

FEDS-PI Workflow

- Data Preparation: hardware engineers upload simulation data (layout, BOM, stackup) to the system.

- Power Network Selection and Database Creation: Users select or edit the power network to be simulated and simulation engineer will establish a database aligned with the chipset's PI design requirements.

- Automated Simulation: The system automatically links to simulation software, executes the simulation based on the configured settings, and generates a report upon completion.

- Design Optimization: Users can optimize the design based on the report's findings and re-run simulations for verification.

- Historical Data Storage: The system stores simulation history, enabling comparisons between different design iterations for continuous PI design improvement.

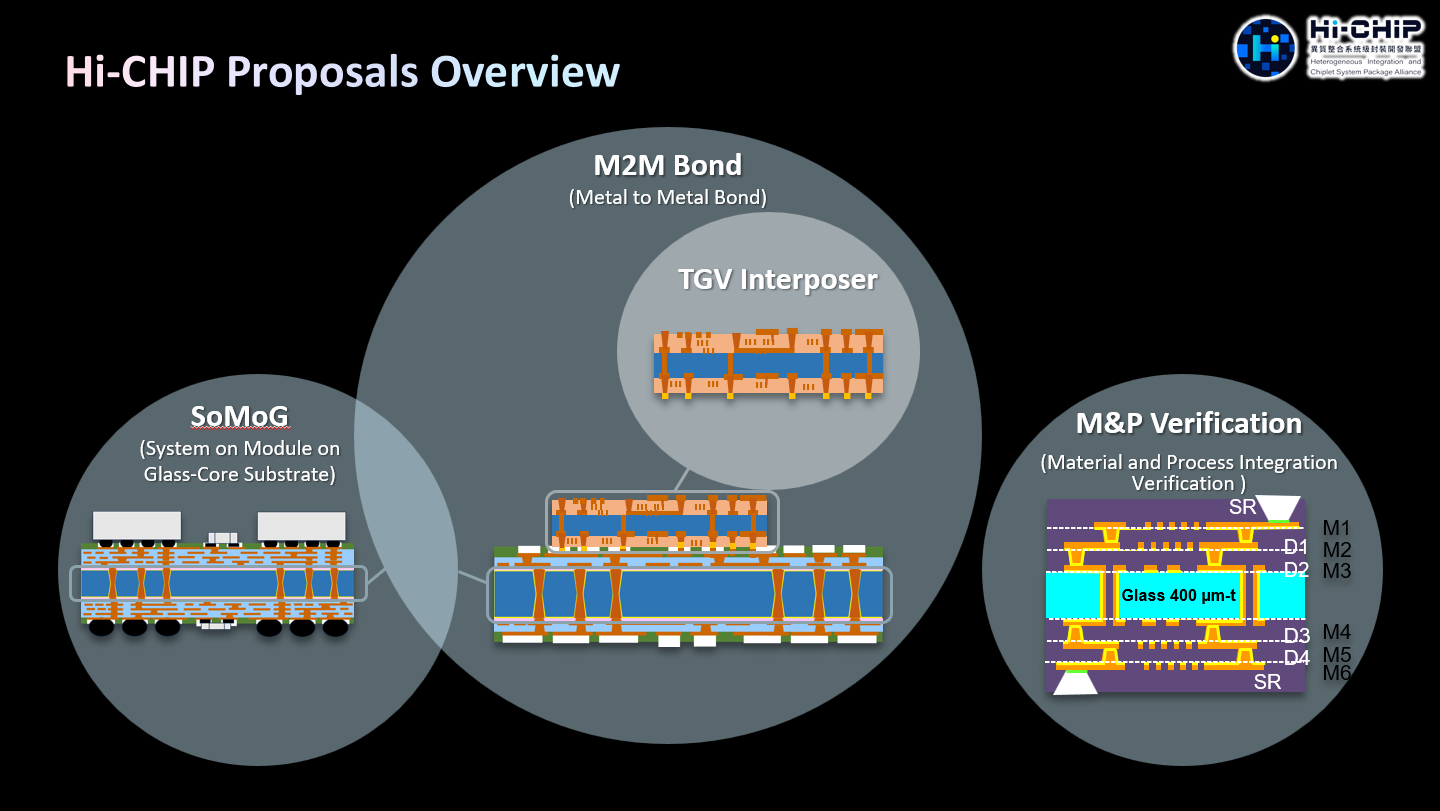

Figure2. Power Integrity Simulation System FEDS-PI Flowchart

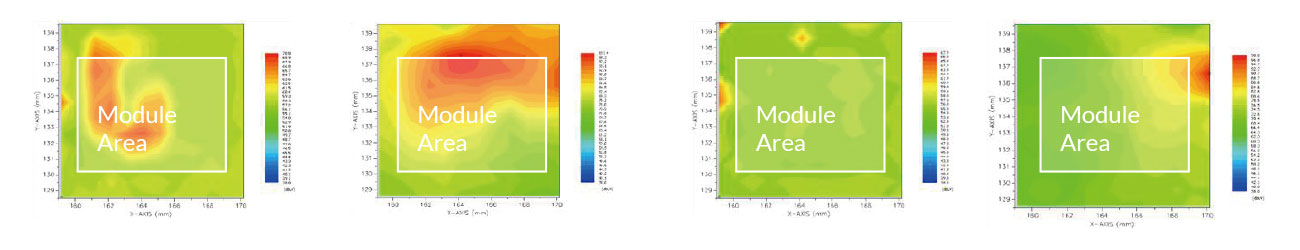

Results

The Power Integrity Simulation System effectively handles a large volume of simulation needs, providing a user-friendly interface that allows engineers to complete simulations independently without complex setups, saving manpower costs. Combined with an optimized workflow, it can quickly diagnose and resolve power issues, shortening the work cycle and improving design quality. Compared to traditional manual simulation methods, the Power Integrity Simulation System demonstrates the following three significant advantages:

- Time Efficiency: Traditional manual simulations are time-consuming, taking 12 working hours from setup to report generation. FEDS-PI reduces the entire process to just 2 hours, significantly improving efficiency by 83%.

- Reliability: Manual simulations are prone to errors, leading to unstable results. FEDS-PI's automated process ensures consistency and stability, and it has built-in error checking mechanisms that can detect potential issues such as open circuits or short circuits after layout upload, providing timely warnings and significantly reducing the risk of human error.

- Simulation Resource Utilization: Traditional methods require both engineers and software licenses for each simulation, while FEDS-PI only requires file uploads and simulation item selection, and the system can automatically complete the simulation. FEDS-PI only requires one software license and one server to operate 24 hours a day, improving resource utilization.

Through the "Power Integrity Simulation System" and the optimized power design strategy, the root cause of power problems can be clearly identified. Modifications can be quickly simulated and verified, significantly shortening the overall problem-solving cycle, improving overall simulation efficiency, and enhancing product design quality. It effectively solves many challenges faced by traditional manual simulations, such as time, manpower, and error rates, providing a highly efficient and reliable design platform for the development process.

Keep up with top trending topic

For the latest innovation technology, application

and industry insight.

Subscribe Our Blog

For the latest innovation technology, application

and industry insight.