Search

- 09/10/2024

Event|USI to Deliver Cutting-edge Integrated Voltage Regulator Module Technology at the Heterogeneous Integration Global Summit

(2024-09-10) On September 5th, USI CTO John Fang delivered cutting-edge Integrated Voltage Regulator Module (IVRM) technology at the "Heterogeneous Integration Global Summit" during SEMICON Taiwan 2024. This innovative technology is poised to power high-performance computing for artificial intelligence (AI) and machine learning (ML).

With the rise of AI, heterogeneous integration is leading the way for future developments. SEMICON Taiwan 2024 featured a three-day "2024 Heterogeneous Integration International Summit" joined by top-notch speakers from industry and academia who talked about how generative AI is transforming chip-making and driving process optimization, and how to create opportunities and breakthroughs in the AI value chain through the latest smart manufacturing technology. Dr. John Fang emphasized that both AI and ML, especially large-scale AI servers, are energy-hungry and need more efficient solutions. As a solution provider, reducing power loss and improving power efficiency at the chip level is our primary focus.

High-performance integrated systems require high power to be delivered to points- of-load (POLs) at high current density. Vertical power delivery and placing power conversion closer to POLs can significantly improve the overall efficiency of the power delivery system. Space constraints are another challenge. For instance, upgrading from a 320W to a 400W chipset requires increasing the phase design from 8 to 10, which poses a significant challenge in terms of space. Therefore, a vertically integrated solution is desirable.

The evolution of power solutions for high-performance computing (HPC) systems started with discrete power components placed side by side on a circuit board. Subsequently, multiple components were integrated into a power module and moved below the circuit board to shorten current paths. Further advancements involved using vertically stacked SiP technology to integrate multi-phase voltage regulator modules, improving power efficiency, density, reliability, and space utilization to meet the growing demands of high-performance computing.

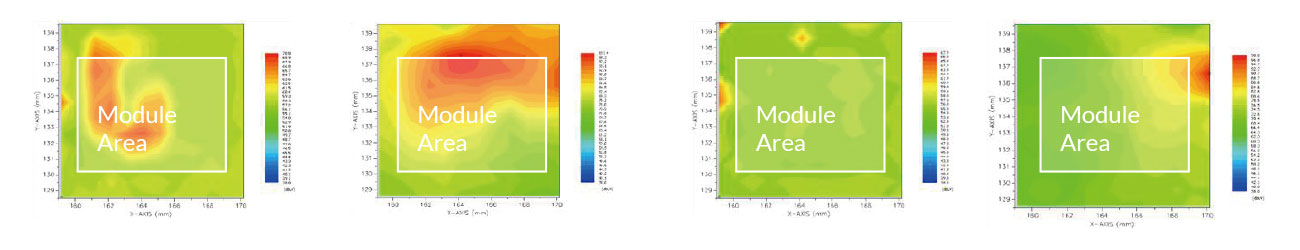

Currently, there are five types of stacked power modules, with 1 piece metal clip, with 1 side or 4 side pin headers and with a piece stand PCB, each using different methods to address high current transmission. A motherboard-less, vertically integrated voltage regulator module can achieve multi-phase voltage regulation, directly placing the voltage regulator module below the System-on-Chip (SoC), shortening current flow distance and reducing copper losses. Compared to the traditional side-by-side placement, current density increases by 50% from 0.4A/mm² to 0.6A/mm², and routing power loss decreases from 12% to 6%.

By vertically integrating components to reduce the horizontal footprint and module height, and utilizing heterogeneous integration and high-density packaging technologies, components can be densely packed in a smaller space. Furthermore, embedding chips directly into the substrate reduces connection layers and parasitic capacitance, lowering resistance and thermal resistance. This leads to improved performance, reliability, and reduced power consumption, representing the future trend in integrated voltage regulator module development.

ASE's powerSiP™ platform is an example of an innovative transformative power delivery platform that reduces signal and transmission losses while addressing current density challenges. It enables vertically integrated multi-stage voltage regulator modules (VRM) for higher system efficiency and lower power consumption.

USI MCC Miniaturization Competence Center has the capability to encompass heterogeneous integration of various components into complex modules, utilizing mature packaging and molding technologies to enable flexible modularization for customers’ various applications".

At the end, CTO John Fang was on behalf of USI participating in the panel discussion, chaired by ASE VP Dr. C.P. Hung, alongside Dr. Eric Beyne from imec, Dr. Debendra Das Sharma from Intel, Dr. Byung Joon (BJ) Han from Silicon Box, and Mr. Kite Huang from UMC. The panel discussion focused on addressing the challenges of the AI era, emphasizing the need to leverage AI tools for improved efficiency, time management, and energy usage".

With the rise of AI, heterogeneous integration is leading the way for future developments. SEMICON Taiwan 2024 featured a three-day "2024 Heterogeneous Integration International Summit" joined by top-notch speakers from industry and academia who talked about how generative AI is transforming chip-making and driving process optimization, and how to create opportunities and breakthroughs in the AI value chain through the latest smart manufacturing technology. Dr. John Fang emphasized that both AI and ML, especially large-scale AI servers, are energy-hungry and need more efficient solutions. As a solution provider, reducing power loss and improving power efficiency at the chip level is our primary focus.

High-performance integrated systems require high power to be delivered to points- of-load (POLs) at high current density. Vertical power delivery and placing power conversion closer to POLs can significantly improve the overall efficiency of the power delivery system. Space constraints are another challenge. For instance, upgrading from a 320W to a 400W chipset requires increasing the phase design from 8 to 10, which poses a significant challenge in terms of space. Therefore, a vertically integrated solution is desirable.

The evolution of power solutions for high-performance computing (HPC) systems started with discrete power components placed side by side on a circuit board. Subsequently, multiple components were integrated into a power module and moved below the circuit board to shorten current paths. Further advancements involved using vertically stacked SiP technology to integrate multi-phase voltage regulator modules, improving power efficiency, density, reliability, and space utilization to meet the growing demands of high-performance computing.

Currently, there are five types of stacked power modules, with 1 piece metal clip, with 1 side or 4 side pin headers and with a piece stand PCB, each using different methods to address high current transmission. A motherboard-less, vertically integrated voltage regulator module can achieve multi-phase voltage regulation, directly placing the voltage regulator module below the System-on-Chip (SoC), shortening current flow distance and reducing copper losses. Compared to the traditional side-by-side placement, current density increases by 50% from 0.4A/mm² to 0.6A/mm², and routing power loss decreases from 12% to 6%.

By vertically integrating components to reduce the horizontal footprint and module height, and utilizing heterogeneous integration and high-density packaging technologies, components can be densely packed in a smaller space. Furthermore, embedding chips directly into the substrate reduces connection layers and parasitic capacitance, lowering resistance and thermal resistance. This leads to improved performance, reliability, and reduced power consumption, representing the future trend in integrated voltage regulator module development.

ASE's powerSiP™ platform is an example of an innovative transformative power delivery platform that reduces signal and transmission losses while addressing current density challenges. It enables vertically integrated multi-stage voltage regulator modules (VRM) for higher system efficiency and lower power consumption.

USI MCC Miniaturization Competence Center has the capability to encompass heterogeneous integration of various components into complex modules, utilizing mature packaging and molding technologies to enable flexible modularization for customers’ various applications".

At the end, CTO John Fang was on behalf of USI participating in the panel discussion, chaired by ASE VP Dr. C.P. Hung, alongside Dr. Eric Beyne from imec, Dr. Debendra Das Sharma from Intel, Dr. Byung Joon (BJ) Han from Silicon Box, and Mr. Kite Huang from UMC. The panel discussion focused on addressing the challenges of the AI era, emphasizing the need to leverage AI tools for improved efficiency, time management, and energy usage".

Keep up with top trending topic

For the latest innovation technology, application

and industry insight.

Subscribe Our Blog

For the latest innovation technology, application

and industry insight.